Разработка цифровых ИС на примере микроконтроллерного ядра SCR1 - верификация и тестирование

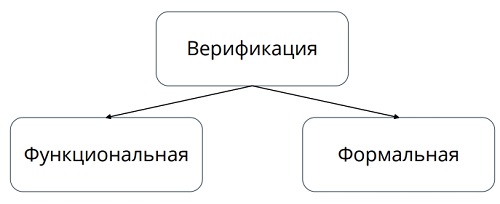

Верификация

Верификация - обоснованная оценка соответствия устройства заданной на него спецификации.

Функциональная верификация

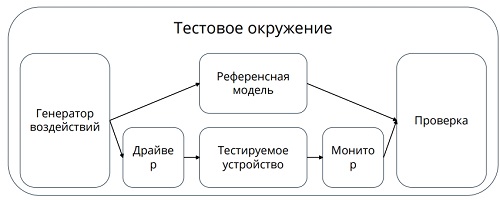

Функциональная верификация предполагает проверку устройства путем подачи входных воздействий и отслеживания отклика.

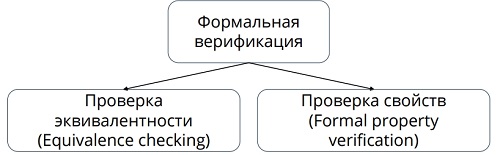

Формальная верификация

Для ознакомления с подходами к функциональной верификации RISC-V ядер рекомендуется изучить курс "Введение в функциональную верификацию RISC-V ядер" преподавателя НИУ МИЭТ Чусова Сергея Андреевича: https://github.com/riscv-tests-intro/riscv-tests-intro

Формальная верификация использует математические методы для доказательства корректного поведения устройства.

Проверка эквивалентности (Equivalence checking) подразумевает сравнение двух версий дизайна. Некоторые виды сравнений:

- RTL - RTL

- Нетлист - RTL

- Нетлист - нетлист

Проверка свойств проверяет соответствует ли дизайн некоторым заданным свойствам. Данные свойства можно задать при помощи SystemVerilog Assertions (SVA).

Основные конструкции SVA

Assertions бывают немедленными (immediate) и конкурентными (concurrent) Immediate assertions вызываются внутри процедурных блоков и являются аналогом if. Concurrent assertions позволяют проверять последовательности событий, распределенных во времени.

assert - определяет обязательное свойство дизайна, которое должно быть проверено. ПО формальной верификации считает, что assert не может быть нарушен и пытается найти контрпример, когда assert нарушается.

Пример concurrent assertions, проверяющий, что подтверждение запроса (ack = 1) приходит через три такта после запроса (req = 1):

assert property (@(posedge clk) req |-> ##3 ack);

assume с точки зрения симуляции эквивалентен assert. С точки зрения ПО формальной верификации assume указывает, что некоторые условия гарантированно истинны. Это позволяет накладывать некоторые ограничения, например, на входные воздействия. Пример, накладывающий ограничения на операционный код инструкции:

assume property (@(posedge clk) opcode == OP_ADD);

Конструкция restrict накладывает ограничения на рассматриваемые ПО формальной верификации сценарии работы устройства. Данная конструкция игнорируется симуляторами и не имеет блока действия.

Пример, аналогичный конструкции assume:

restrict property (@(posedge clk) opcode == OP_ADD);

Конструкция cover проверяет, были ли достигнуты некоторые состояния устройства. Если данное состояние не было достигнуто, симуляция не выдаст ошибку. Приведем пример, проверяющий было ли достигнуто такое состояние, что подтверждение запроса (ack = 1) пришло через три такта после запроса (req = 1):

cover property (@(posedge clk) req |-> ##3 ack);

Пример симуляции микропроцессорного ядра SCR1

Микропроцессорное ядро "Syntacore SCR1" поставляется вместе с комплектом тестовых программ для проверки работоспособности ядра в специальных программах-симуляторах. Далее будут описаны шаги по установке необходимого ПО и пакетов для успешного запуска встроенных тестов. Шаги будут описаны для Ubuntu 22.04 LTS.

Установка git и клонирование репозитория SCR1

Установка git осуществляется командой:

sudo apt install git -y

Клонирование репозитория:

git clone https://github.com/syntacore/scr1.git

Инициализация подмодулей:

cd scr1/ git submodule update --init -recursive

Необходимое ПО

В каталоге "docs" клонированного репозитория содержится руководство пользователя "scr1_um.pdf", в котором описано необходимое ПО и некоторые шаги по его установке. Для запуска встроенных тестов необходимы:

- Кросскомпилятор RISC-V GCC;

- Поддерживаемая программа-симулятор, в данном случае будет использоваться симулятор с открытым исходным кодом "Verilator".

RISC-V GCC

Установка библиотек и утилит:

sudo apt-get install libusb-dev libftdi1* sudo apt-get install make

Далее необходимо скачать архив с готовым RISC-V GCC по ссылке: https://syntacore.com/tools/development-tools и распаковать с помощью команды:

tar xf <archive_name>.tar.gz

Далее необходимо открыть файл ".bashrc"

cd ~ gedit .bashrc

И добавить в конец файла строку:

.<sc-dt_install_path>/env.s

Verilator

Текущей поддерживаемой версией Verilator является версия v4.102. Подробно шаги по установке приведены по ссылке: https://verilator.org/guide/latest/install.html#detailed-build-instructions.

Установка необходимых пакетов:

sudo apt-get install git help2man perl python3 make sudo apt-get install g++ sudo apt-get install libfl2 # ignore if gives error sudo apt-get install libfl-dev # ignore if gives error sudo apt-get install zlibc zlib1g zlib1g-dev # ignore if gives error

Установка необходимых пакетов:

sudo apt-get install ccache sudo apt-get install mold sudo apt-get install libgoogle-perftools-dev numactl sudo apt-get install perl-doc sudo apt-get install git autoconf flex bison

Клонирование репозитория и переход на нужную версию

git clone https://github.com/verilator/verilator cd verilator git checkout v4.102

Создание конфигурационного скриптового файла:

autoconf

Настройки для глобальной установки:

unset VERILATOR_ROOT ./configure

Клонирование репозитория и переход на нужную версию

git clone https://github.com/verilator/verilator cd verilator git checkout v4.102

Создание конфигурационного скриптового файла:

autoconf

Настройки для глобальной установки:

unset VERILATOR_ROOT ./configure

Компиляция Verilator:

make -j `nproc`

Запуск теста для проверки компиляции:

make test

Установка Verilator (в случае успеха прошлой команды), может понадобиться запуск от имени root (добавить sudo в начало команды) make install