Разработка цифровых ИС на примере микроконтроллерного ядра SCR1 - верификация и тестирование

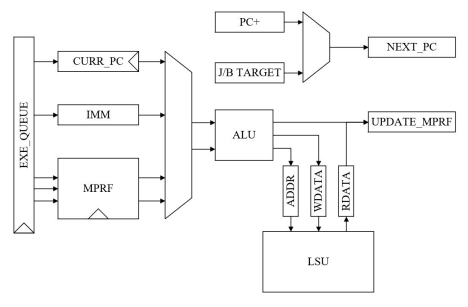

Выполнение инструкции

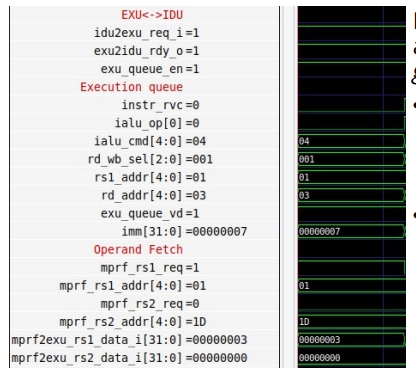

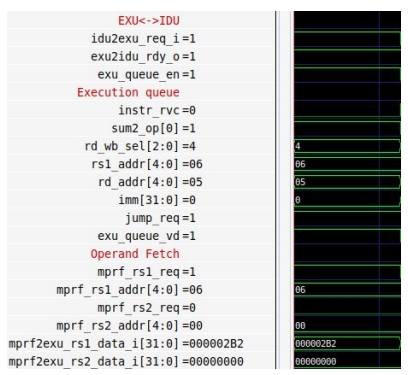

Когда стадия декодирования готова передать декодированную инструкцию (idu2exu_req_i = 1), а стадия выполнения готова ее принять (exu2idu_rdy_o = 1), выставляется флаг "exu_queue_en", сигнализирующий о записи данных в конвейерный регистр стадии выполнения (передаётся структура типа "type_scr1_exu_cmd_s"). Далее будет рассмотрено выполнение инструкций, использованных ранее.

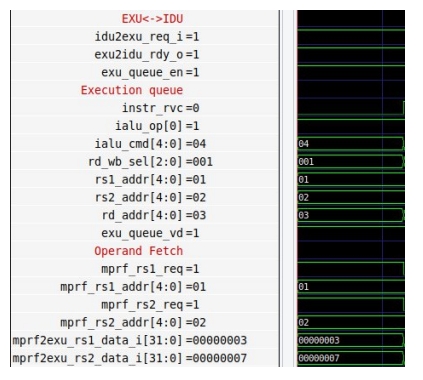

Выполнение инструкции (R-тип)

Рассмотрим выполнение инструкции "add gp, ra, sp" (0x002081B3).

Декодированная инструкция (управляющие сигналы, адреса операндов и т.д.) направляется на стадию выполнения.

Из регистрового файла считываются операнды: "rs1" = 3, "rs2" = 7.

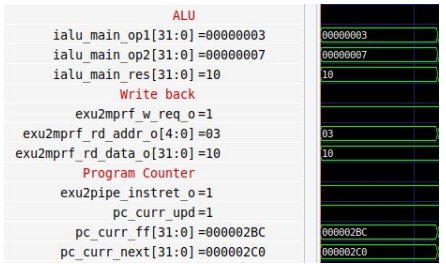

Считанные операнды направляются в АЛУ с указанием операции, в данном случае - сложение.

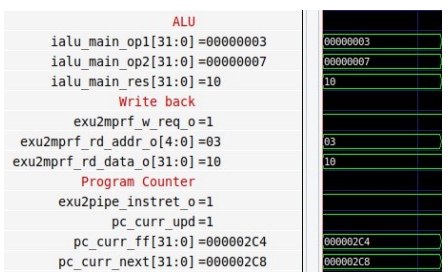

АЛУ вычисляет результат операции (ialu_main_res = 10).

В регистровый файл отправляется запрос на запись результата (exu2mprf_w_req_o) с указанием адреса (exu2mprf_rd_addr_o = 3) и данных (exu2mprf_rd_data_o = 10). С приходом фронта тактового сигнала данные запишутся в MPRF.

По окончании выполнения инструкции (exu2pipe_instret_o = 1) выставляется флаг обновления счетчика инструкций "pc_curr_upd". С приходом фронта тактового сигнала "pc_curr_ff" примет значение "pc_curr_next" (инкрементируется на 4).

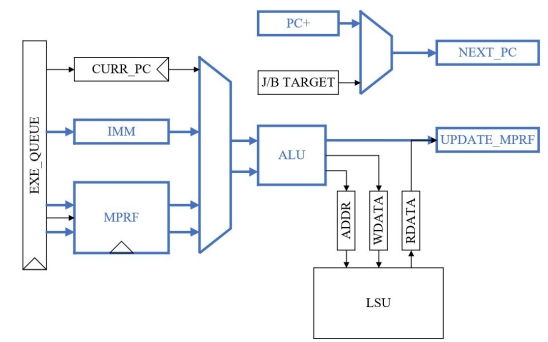

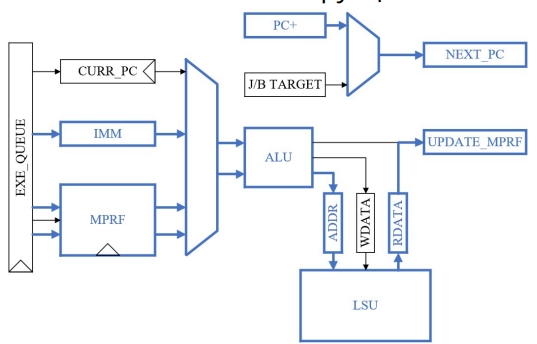

Упрощенная схема выполнения инструкции:

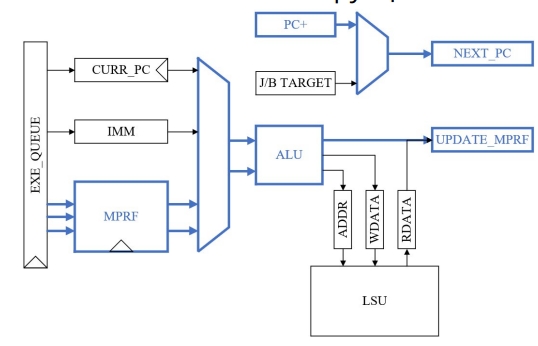

Выполнение инструкции (I-тип, addi)

Рассмотрим выполнение арифметической инструкции I-типа "addi gp, ra, 7" (0x00708193).

- Декодированная инструкция (управляющие сигналы, адреса операндов и т.д.) направляется на стадию выполнения.

- Из регистрового файла считывается только один операнд: "rs1" = 3, т.к. вторым операндом является непосредственное значение (imm = 7).

Дальнейшее выполнение аналогично инструкции "add" за исключением того, что одним из операндов АЛУ является непосредственное значение.

Упрощенная схема выполнения инструкции:

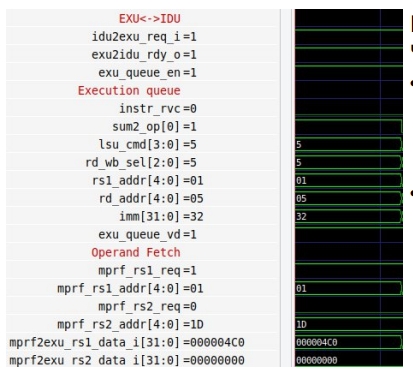

Выполнение инструкции (I-тип, lhu)

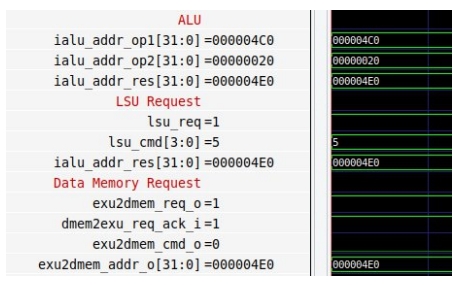

Рассмотрим выполнение инструкции чтения I-типа "lhu t0, 32(ra)" (0x0200D283).

- Декодированная инструкция (управляющие сигналы, адреса операндов и т.д.) направляется на стадию выполнения.

- Из регистрового файла считывается только один операнд: "rs1" = 0x4C0, т.к. вторым операндом является непосредственное значение (imm = 32)

- Операнды i_alu_addr_op1 и i_alu_addr_op2 направляются в сумматор для вычисления адреса чтения (i_alu_addr_res = 0x4E0).

- В модуль чтения/записи (LSU) направляется запрос (lsu_req = 1) на чтение половины слова данных с беззнаковым расширением (lsu_cmd = 5) по ранее вычисленному адресу.

- LSU формирует запрос к памяти данных (exu2dmem_req_o = 1) на чтение (exu2dmem_cmd_o = 0) по адресу exu2dmem_addr_o = 0x4E0. Память данных подтверждает запрос (exu2dmem_req_ack_i = 1)

- На следующем такте (задержка может быть произвольной) приходит ответ от памяти данных об успешности операции (dmem2exu_resp_i = 1) и считанные данные (dmem2exu_rdata_i = 0xFF).

- LSU беззнаково расширяет считанные данные (lsu_l_data = 0xFF) и выставляет флаг их готовности (lsu_rdy = 1)

- Далее, аналогично предыдущим инструкциям, с приходом фронта тактового сигнала результат записывается в MPRF и обновляется счетчик инструкций.

Упрощенная схема выполнения инструкции:

Выполнение инструкции (I-тип, jalr)

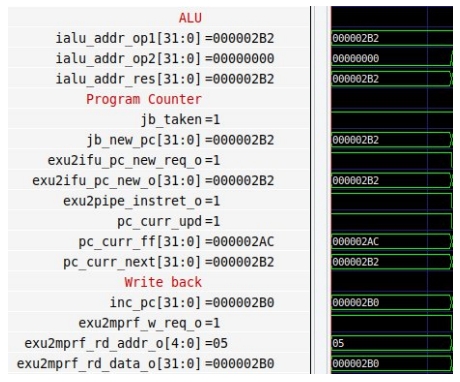

Рассмотрим выполнение инструкции прыжка I-типа "jalr t0, t1" (0x000302E7).

- Декодированная инструкция (управляющие сигналы, адреса операндов и т.д.) направляется на стадию выполнения.

- Из регистрового файла считывается только один операнд: "rs1" = 0x2B2, т.к. вторым операндом является непосредственное значение (imm = 0).

- Операнды i_alu_addr_op1 и i_alu_addr_op2 направляются в сумматор для вычисления адреса прыжка (i_alu_addr_res = 0x2B2).

- Блок выполнения передает блоку выборки флаг запроса нового адреса инструкции (exu2ifu_pc_new_req_o = 1) и сам адрес (exu2ifu_pc_new_o = 0x2B2).

- При этом инкрементированное значение счетчика инструкций (inc_pc = 0x2B0) запишется в регистр-назначение.

- Поскольку все инструкции, считанные после "jalr", необходимо отбросить, формируется сигнал очистки очереди инструкций (q_flush_req = 1).

- Так как адрес 0x2B2 не выровнен на 4 байта, выставляется флаг невыровненного счетчика инструкций (new_pc_unaligned_next = 1).

- В таком случае адрес запроса в память инструкций будет 0x2B0.

Упрощенная схема выполнения инструкции: