Опубликован: 04.08.2025 | Доступ: свободный | Студентов: 12 / 0 | Длительность: 02:58:00

Лекция 3:

Разработка цифровых ИС на примере микроконтроллерного ядра SCR1 - верификация и тестирование

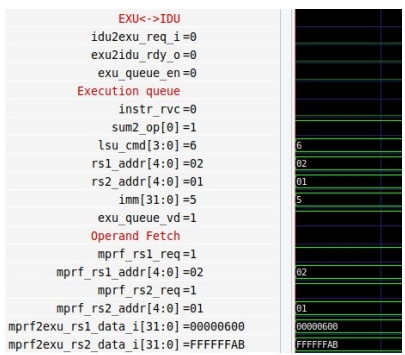

Выполнение инструкции (S-тип)

Рассмотрим выполнение инструкции Sтипа "sb ra, 5(sp)" (0x001102A3).

- Декодированная инструкция (управляющие сигналы, адреса операндов и т.д.) направляется на стадию выполнения.

- Из регистрового файла считывается два операнда: "rs1" = 0x600, "rs2" = 0xFFFFFFAB.

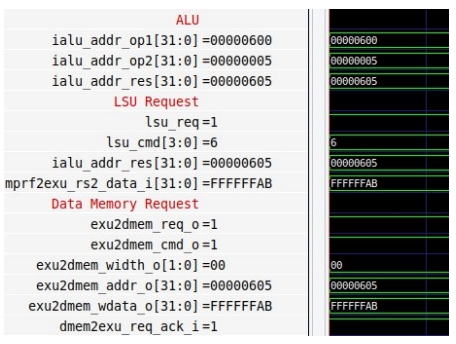

- Операнды i_alu_addr_op1 и i_alu_addr_op2 направляются в сумматор для вычисления адреса записи (i_alu_addr_res = 0x605). Операнды для вычисления адреса - непосредственное значение и регистроперанд rs1.

- В модуль чтения/записи (LSU) направляется запрос (lsu_req = 1) на запись одного байта (lsu_cmd = 6) по ранее вычисленному адресу. Данные для записи - данные из регистра-операнда rs2.

- LSU формирует запрос к памяти данных (exu2dmem_req_o = 1) на запись (exu2dmem_cmd_o = 1) одного байта (exu2dmem_width_o = 0) по адресу exu2dmem_addr_o = 0x605. Память данных подтверждает запрос (exu2dmem_req_ack_i = 1).

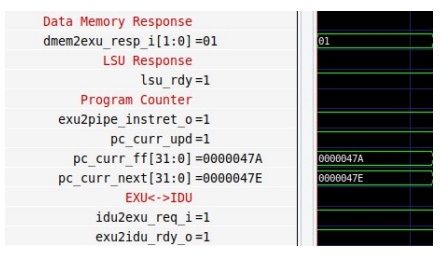

- На следующем такте (задержка может быть произвольной) память данных сообщает об успешности записи (dmem2exu_resp_i = 1).

- LSU выставляет флаг готовности (lsu_rdy = 1).

- Инструкция считается выполненной (exu2pipe_instret_o = 1).

- Блок выполнения готов принять новую инструкцию (exu2idu_rdy_o = 1).

- Счетчик инструкций будет инкрементирован с приходом фронта тактового сигнала.

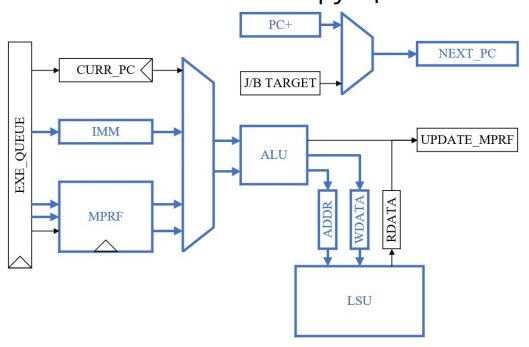

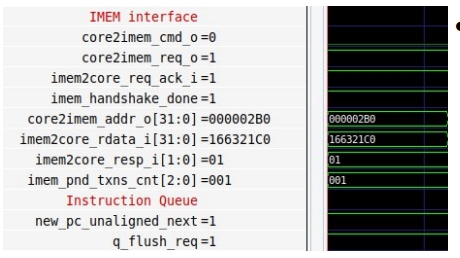

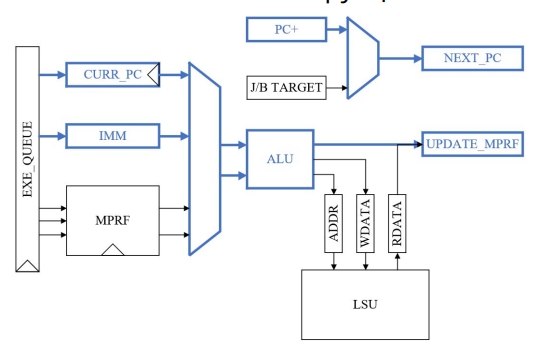

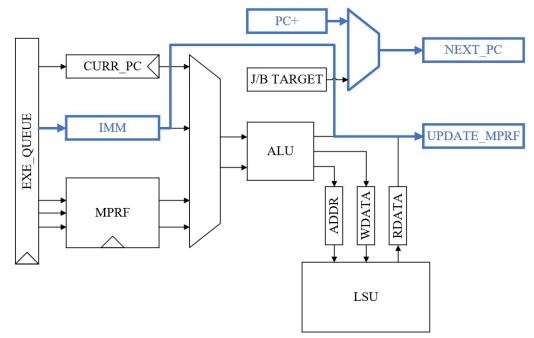

Упрощенная схема выполнения инструкции:

Выполнение инструкции (B-тип)

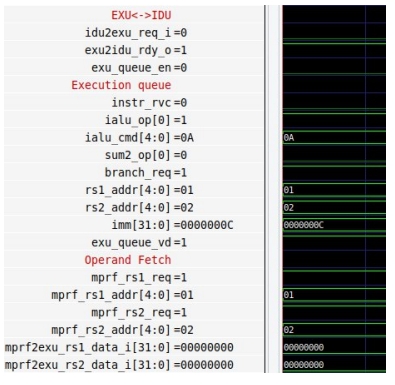

Рассмотрим выполнение инструкции Bтипа "bge ra, sp, 0x2B2" (0x0020D663). При этом адрес инструкции - 0x2A6.

- Декодированная инструкция (управляющие сигналы, адреса операндов и т.д.) направляется на стадию выполнения.

- Из регистрового файла считывается два операнда: "rs1" = 0, "rs2" = 0.

- Считанные операнды i_alu_main_op1 и i_alu_main_op2 направляются в АЛУ для их сравнения. Результат сравнения содержит сигнал ialu_cmd = 1

- Адрес ветвления вычисляется в отдельном сумматоре. Операнды - текущее значение счётчика команд и непосредственное значение. Результат: ialu_addr_res = 0x2B2.

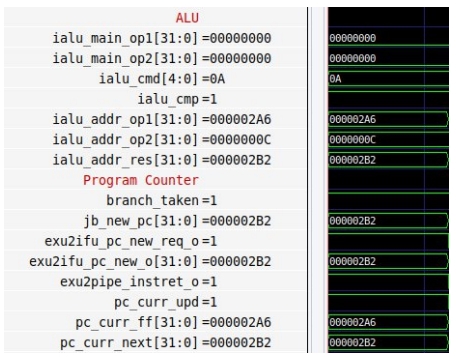

- Так как условие ветвления выполнено (ialu_cmd = 1), блок выполнения передает блоку выборки запрос на новый адрес инструкции (exu2ifu_pc_new_req_o = 1) и сам адрес (exu2ifu_pc_new_o = 0x2B2).

- Данное значение с приходом фронта тактового сигнала также примет счётчик инструкций. 80 Выполнение инструкции (B-тип)

- Аналогично инструкции "jalr" необходимо очистить очередь инструкций и передать памяти инструкций запрос по новому адресу.

Упрощенная схема выполнения инструкции:

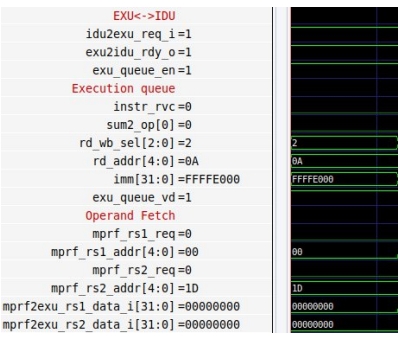

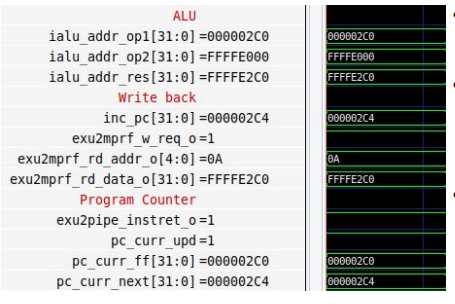

Выполнение инструкции (U-тип, auipc)

Рассмотрим выполнение инструкции Uтипа "auipc a0, 0xFFFFE" (0xFFFFE517). При этом адрес инструкции - 0x2C0.

- Декодированная инструкция (управляющие сигналы, адреса операндов и т.д.) направляется на стадию выполнения.

- Выборка операндов из MPRF не требуется.

- Операндами в данном случае являются счетчик инструкций и непосредственное значение.

- Операнды "i_alu_addr_op1" и "i_alu_addr_op2" направляются в сумматор для вычисления результата (i_alu_addr_res = 0xFFFFE2C0).

- С приходом фронта тактового сигнала вычисленный результат запишется в регистр-назначение в MPRF, а счетчик инструкций инкрементируется.

Упрощенная схема выполнения инструкции:

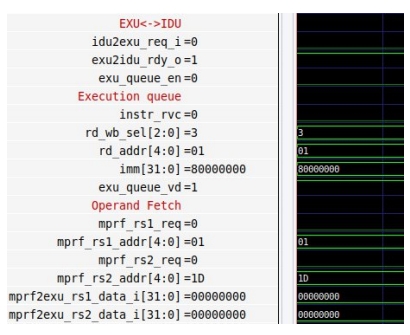

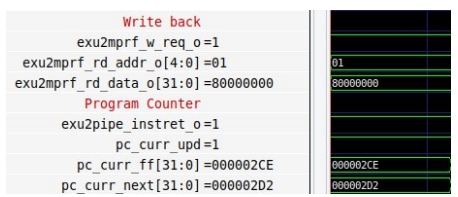

Выполнение инструкции (U-тип, lui)

Рассмотрим выполнение инструкции Uтипа "lui ra, 0x80000" (0x800000B7).

- Декодированная инструкция (управляющие сигналы, адреса операндов и т.д.) направляется на стадию выполнения.

- Выборка операндов из MPRF не требуется.

- С приходом фронта тактового сигнала в MPRF записывается непосредственное значение, а программный счетчик инкрементируется.

Упрощенная схема выполнения инструкции: