Разработка цифровых ИС на примере микроконтроллерного ядра SCR1 - верификация и тестирование

Выполнение инструкции (J-тип)

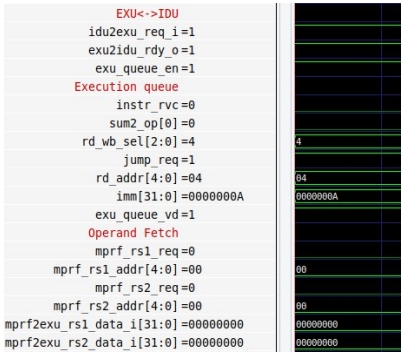

Рассмотрим выполнение инструкции прыжка J-типа "jal tp, 2AE" (0x00A0026F). "jal tp, 2AE". При этом адрес инструкции - 0x2A4.

- Декодированная инструкция (управляющие сигналы, адреса операндов и т.д.) направляется на стадию выполнения.

- Выборка операндов из MPRF не требуется.

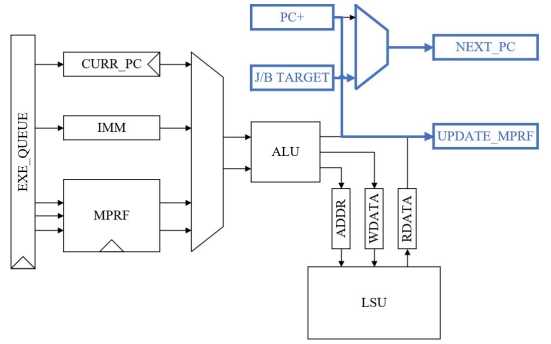

- Операндами в данном случае являются счетчик инструкций и непосредственное значение.

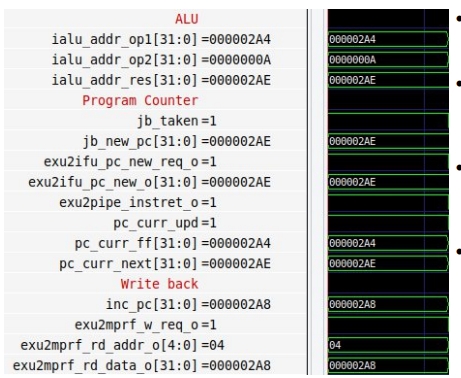

- Операнды "i_alu_addr_op1" и "i_alu_addr_op2" направляются в сумматор для вычисления адреса прыжка (i_alu_addr_res = 0x2AE).

- Блок выполнения передает блоку выборки флаг запроса нового адреса инструкции (exu2ifu_pc_new_req_o = 1) и сам адрес (exu2ifu_pc_new_o = 0x2AE).

- При этом инкрементированное значение счетчика инструкций (inc_pc = 0x2A8) запишется в регистрназначение.

- Аналогично инструкции "jalr" необходимо очистить очередь инструкций и передать памяти инструкций запрос по новому адресу.

Упрощенная схема выполнения инструкции:

Исключения

В случае возникновения "необычного" состояния во время работы ядра формируется т.н. исключение.

Зачастую, возникновение исключения конвертируется в ловушку, т.е. управление будет передано контролирующую среду.

Рассмотрим пример возникновения исключения некорректной инструкции (Illegal Instruction).

Illegal Instruction

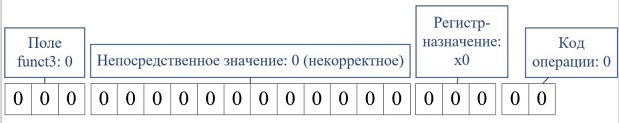

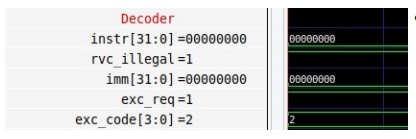

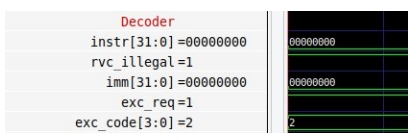

Рассмотрим некорректную инструкцию 0x00000000. Код операции и поле funct3 соответствуют RVC инструкции CIW-типа c.addi4spn, добавляющей непосредственное значение, умноженное на 4, к регистру указателя стэка sp и записывающей полученное значение в регистр rd. Отличие от корректной инструкции - нулевое непосредственное значение.

- При попадании такой инструкции в декодер, сначала она будет воспринята, как RVC инструкция c.addi4spn, так как операционный код и поле funct3 заполнены нулями. Но из-за нулевого непосредственного значения будет сгенерирован флаг "rvc_illegal".

- Рассмотренные ранее поля структуры типа "type_scr1_exu_cmd_s" заполнятся "безопасными" значениями, т.е. флаги записи/чтения в регистры и память, флаги ветвлений, прыжков и т.д. будут сняты.

- Сама инструкция будет записана в непосредственное значение.

- При возникновении исключения также заполняются поля "exc_req" и "exc_code" структуры типа "type_scr1_exu_cmd_s", которые ранее были опущены.

- "exc_req" - флаг возникновения исключения.

- "exc_code" - код исключения, в данном случае код 2 говорит о возникновении исключения "Illegal Instruction"

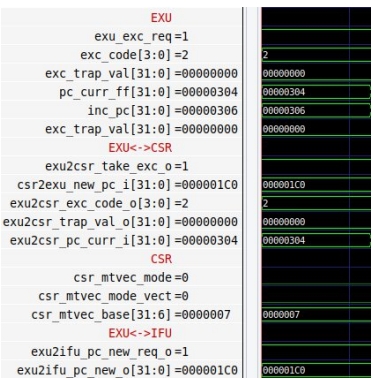

При возникновении исключения некорректной инструкции блок выполнения передаст в блок CSR:

- Флаг возникновения исключения (exu2csr_take_exc = 1)

- Код исключения (exu2csr_exc_code = 2)

- Инструкцию, вызвавшую исключение (exu2csr_trap_val = 0x00000000).

- Текущее значение счетчика инструкций, т.е. адрес инструкции, вызвавшей исключение.

В ответ на этом же такте блок выполнения получит новое значение счетчика инструкций, т.н. trap vector (csr2exu_new_pc = 0x1C0).

Механизм формирования trap vector'а может быть прямым и векторным (зависит от конфигурации ядра и младшего бита CSRрегистра MTVEC).

Для исключений, независимо от механизма формирования trap vector'а, новое значение счетчика инструкций будет равно конкатенации "csr_mtvec_base" (поле BASE CSRрегистра MTVEC) и шести нулей.

В данном случае получим адрес 0x1C0, который будет отправлен в блок выборки.

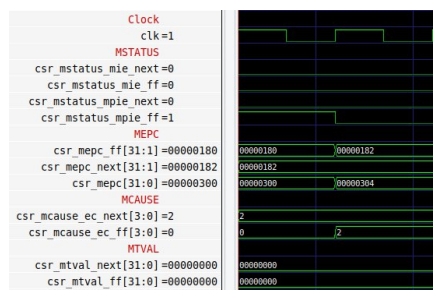

Рассмотрим изменение CSRрегистров при возникновении исключения некорректной инструкции.

На картинке представлено два такта. Первый относится к такту, когда исключение было обработано блоком выполнения и данные переданы в CSR блок. Второй - следующий такт.

- Поле MIE регистра MSTATUS, отвечающее за включение прерываний, будет установлено в 0 (csr_mstatus_mie_ff).

- Предыдущее значение MIE будет записано в поле MPIE регистра MSTATUS (csr_mstatus_mpie_ff).

- В регистр MEPC будет записан адрес инструкции, вызвавшей исключение (csr_mepc = 0x304).

- В поле EC регистра MCAUSE будет записан код исключения (csr_mcause_ec_ff = 2).

- В регистр MTVAL будет записана инструкция, вызвавшая исключение (csr_mtval_ff = 0x00000000).

Список использованных источников

- SCR1 External Architecture Specification - URL: https://github.com/syntacore/scr1/blob/master/docs /scr1_eas.pdf.

- SCR1 User Manual - URL: https://github.com/syntacore/scr1/blob/master/docs /scr1_um.pdf.