Разработка цифровых ИС на примере микроконтроллерного ядра SCR1 - HDL описание

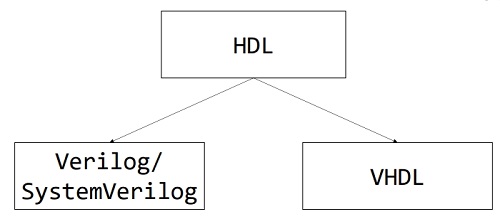

Что такое HDL HDL

(Hardware Description Language) - язык описания аппаратуры, использующийся для описания структуры и поведения цифровой интегральной схемы.

Основное отличие от языков программирования - описание параллелизмов процессов в цифровой ИС.

Наиболее популярные языки

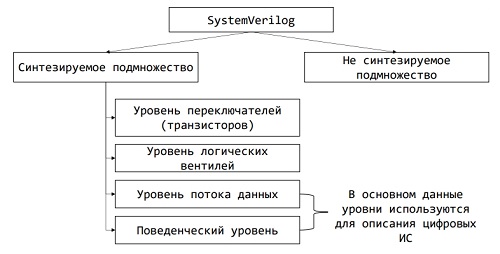

Основные конструкции SystemVerilog

Модули в SystemVerilog

- Основной строительный блок в Verilog.

- Содержит HDL-описание (на любом из 4-х уровней абстракции) устройства, а также т.н. "инстансы" (экземпляры других модулей).

- Взаимодействует с внешней средой моделирования/реализации только через порты; внутренности модуля скрыты от окружающей среды.

Уровень потока данных

На уровне потока данных устройство описывается в терминах обработки данных и математических/логических операций.

Основная конструкция - постоянное присваивание (ключевое слово "assign").

Пример мультиплексора 2-в-1:

assign out = sel ? in1 : in2;

Поведенческий уровень

- Высокий уровень абстракции -> проще сконцентрироваться на архитектуре проекта.

- Схож с программированием на языке высокого уровня (возможно использование конструкций if/else, for, case и т.д.).

- Гибкие лексические конструкции.

- Могут быть ошибки вследствие гибкости синтаксических конструкций.

Основные синтезируемые поведенческие конструкции - процедурные блоки:

- always_ff (последовательностная логика с управлением перепадом).

- always_latch (последовательностная логика с потенциальным управлением).

- always_comb (комбинационная логика).

Пример описания мультиплексора 2-в-1:

always_comb

case(sel)

1'b0: in1;

1'b1: in2;

endcase

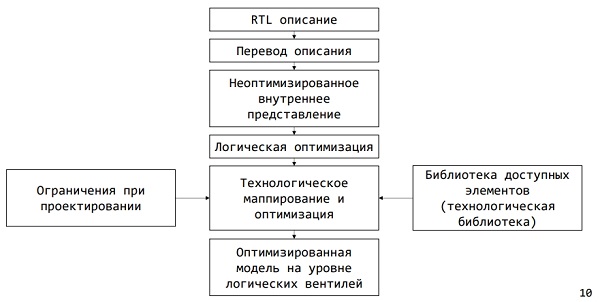

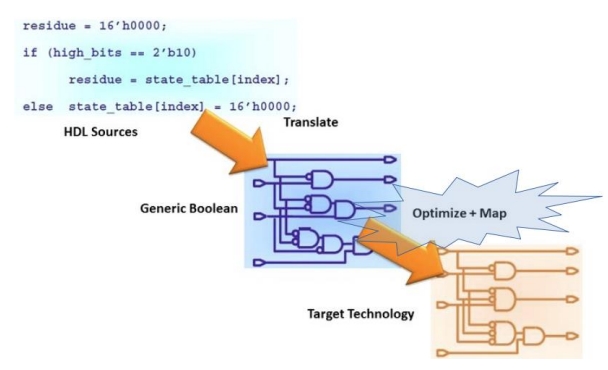

Логический синтез

Обзор микропроцессорного ядра SCR1

Микропроцессорное ядро "Syntacore "SCR1" - открытое микропроцессорное ядро на базе открытой архитектуры RISC-V.

Поддерживаемые базовые расширения:

- RV32I - 32 целочисленных регистра, 47 целочисленных инструкций.

- RV32E - 16 целочисленных регистров, 47 целочисленных инструкций.

Поддерживаемые расширения:

- RVM - инструкции целочисленного умножения и деления.

- RVC - сжатые 16-ти битные инструкции.

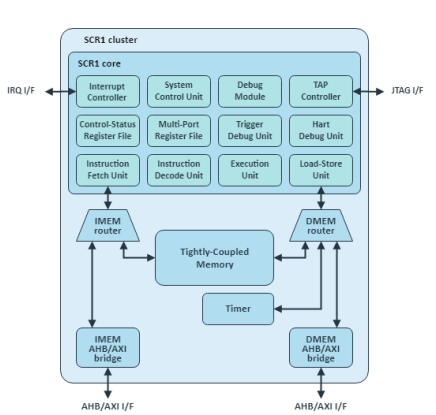

Кластер SCR1

Кластер SCR1 содержит:

- Микропроцессорное ядро (SCR1 core);

- Маршрутизаторы памяти данных (DMEM router) и памяти инструкций (IMEM router);

- Тесно-связанную память (Tightly-Coupled Memory);

- Машинный таймер (Timer);

- Мосты для внешних AXI/AHB интерфейсов памяти инструкций и данных (IMEM/DMEM AXI/AHB bridge).

Конвейер обработки инструкций

SCR1 содержит простой конвейер, обрабатывающий инструкции строго по порядку и состоящий из следующих фаз:

- Запрос инструкции;

- Получение инструкции;

- Декодирование инструкции;

- Выборка операндов;

- Арифметические и логические операции;

- Операции загрузки/сохранения в память данных;

- Управление потоком инструкций (расчёт следующего значение счетчика команд);

- Запись результатов;