Разработка цифровых ИС на примере микроконтроллерного ядра SCR1 - HDL описание

Управление потоком инструкций

Во время данной фазы вычисляется следующее значение программного счетчика.

Обычно, значение программного счетчика увеличивается на 4 для 32-битных инструкций и на 2 для 16-битных инструкций. Исключением являются инструкции прыжка, ветвления, возникновение исключений, прерываний и т.д.

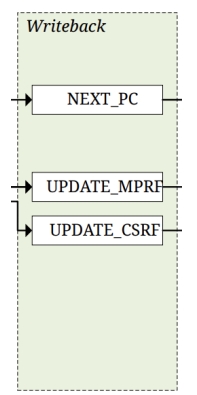

Запись результатов

Во время данной фазы происходит обновление регистров общего назначения (MPRF), регистров контроля и состояния (CSR) и программного счетчика значениями, вычисленными во время выполнения предыдущих фаз.

Конфликты

- Конфликты данных: не возникают, поскольку выборка операндов и фиксация результатов происходит на одной стадии конвейера.

- Структурные конфликты: если несколько инструкций нуждаются в одном аппаратном ресурсе, выполнение более поздней инструкции останавливается до освобождения данного ресурса более ранней инструкцией.

- Конфликты управления: когда конвейеру выполнения инструкций требуется изменить значение программного счетчика на новое значение (не увеличение на 4 или 2), конвейер очищается от последующих инструкций, а выборка начинается с начинается с нового значения программного счетчика.

Конфигурации конвейера

2 стадии:

- Стадия запроса инструкции.

- Стадия получения инструкции, декодирования и выполнения.

3 стадии:

- Стадия запроса инструкции.

- Стадия получения инструкции и декодирования.

- Стадия выполнения инструкции.

4 стадии:

- Стадия запроса инструкции.

- Стадия получения инструкции.

- Стадия декодирования инструкции.

- Стадия выполнения инструкции.

Контроллер прерываний

Микропроцессорное ядро SCR1 имеет опциональный интегрированный программируемый контроллер прерываний (англ. Integrated Programmable Interrupt Controller, IPIC).

Контроллер прерываний поддерживает до 16 линий прерываний (внешний вывод для подключения источника прерывания) и до 16 соответствующих векторов прерываний (номер внешнего прерывания, генерируемый на запрос прерывания). Каждая линия прерывания статически соответствует вектору прерывания.

- Каждый вектор прерывания имеет фиксированный приоритет. Вектор с наименьшим номером имеет высший приоритет.

- Контроллер прерываний поддерживает т.н. вложенные прерывания (англ. nested interrupts), т.е. прерывания, возникшие во время обработки другого прерывания и имеющие более высокий приоритет.

- IPIC поддерживает опциональный 2-х стадийный синхронизатор линий прерываний.

- Программирование IPIC осуществляется с помощью специальных регистров.

Больше информации о IPIC приведено в разделе 7 спецификации SCR1, приведенной в [1].

Подсистема отладки

Подсистема отладки используется для тестирования и управления ядром, а также модулями кластера. Подсистема отладки содержит следующие модули:

- TAP контроллер (TAPC).

- TAP синхронизатор.

- System Control Unit (SCU).

- Debug Module Interface (DMI).

- Debug Module (DM).

- Hart Debug Unit (HDU).

- Trigger Debug Unit (TDU).

TAP контроллер

TAP (Test Access Port) - интерфейс, используемый для отладки и тестирования.

TAP контроллер управляет операциями JTAG и представляет собой конечный автомат с 16 состояниями. Модуль TAP также содержит регистр инструкций и несколько регистров данных, которые и позволяют производить отладку, тестирование и управление ядром.

Больше информации о TAP приведено в разделе 8.2 спецификации SCR1, приведенной в [1].

TAP синхронизатор

Период тактового сигнала JTAG должен быть в 12 и более раз больше, чем тактовый сигнал остальной логики. Таком образом, TAP контроллер и модули, которыми он управляет, находятся в различных тактовых доменах. Для синхронизации данных тактовых доменов используется TAP синхронизатор.

System Control Unit

Данный модуль управляет подсистемой сброса ядра, включая набор регистров управления и состояния и схему сигналов сброса.

Схема сброса осуществляет синхронизацию входных сигналов сброса и обеспечивает необходимые зависимости между входными сигналами сброса, внутренними генерируемыми сигналами сброса и основными продуктами SCU.

Больше информации о SCU приведено в разделе 8.3 спецификации SCR1, приведенной в [1].