Разработка цифровых ИС на примере микроконтроллерного ядра SCR1 - верификация и тестирование

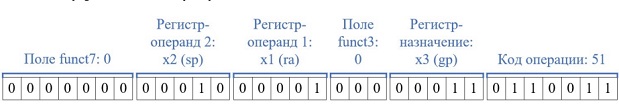

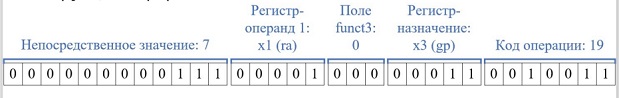

Декодирование инструкции (R-тип)

Рассмотрим декодирование инструкции R-типа на примере инструкции "add gp, ra, sp".

Инструкция в формате "hex": 0x002081B3.

- RVI инструкция (instr_rvc = 0).

- Операндами АЛУ являются значения регистров ra и sp (ialu_op = 1).

- Операция АЛУ - сложение (ialu_cmd = 4).

- Источник данных для MPRF - выход АЛУ (rd_wb_sel = 1).

- Первый регистр-операнд - x1 (rs1_addr = 1).

- Второй регистр-операнд - x2 (rs2_addr = 2).

- Регистр-назначение - x3 (rd_addr = 3).

Остальные поля не имеют значения для инструкций R-типа.

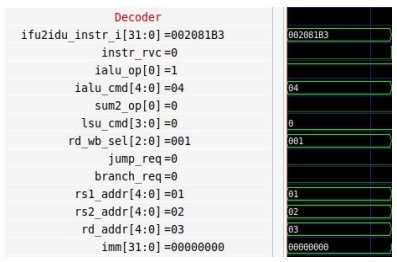

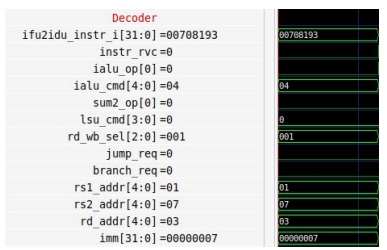

Декодирование инструкции (I-тип, addi)

Инструкции I-типа можно условно разделить на инструкции чтения (lw, lh и т.д.), арифметические и логические инструкции (addi, ori и т.д.) и инструкции прыжка (jalr).

Рассмотрим декодирование арифметической инструкции I-типа на примере инструкции "addi gp, ra, 7".

Инструкция в формате "hex": 0x00708193.

- RVI инструкция (instr_rvc = 0).

- Операндами АЛУ являются значение в регистре ra и непосредственное значение (ialu_op = 0).

- Операция АЛУ - сложение (ialu_cmd = 4).

- Источник данных для MPRF - выход АЛУ (rd_wb_sel = 1).

- Первый регистр-операнд - x1 (rs1_addr = 1).

- Регистр-назначение - x3 (rd_addr = 3).

- Непосредственное значение - 7 (imm = 7).

Остальные поля не имеют значения для данной инструкций.

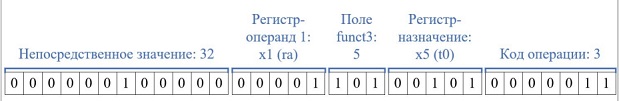

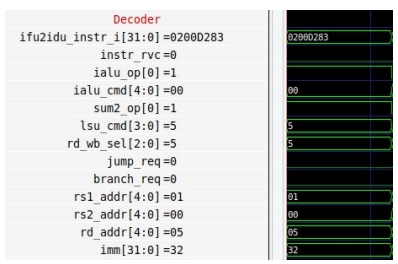

Декодирование инструкции (I-тип, lhu)

Рассмотрим декодирование инструкции чтения I-типа на примере инструкции "lhu t0, 32(ra)".

Инструкция в формате "hex": 0x0200D283.

- RVI инструкция (instr_rvc = 0).

- Вычисление адреса чтения (ra+32) происходит без использования основного АЛУ, а с помощью отдельного сумматора "sum2", по данной причине ialu_cmd = 0.

- Операнды для вычисления адреса чтения - значение в регистре ra и непосредственное значение (sum2_op = 1).

- Тип операции модуля чтения/записи - чтение половины слова данных с беззнаковым расширением до 32 бит (lsu_cmd = 5)

- Источник данных для MPRF - модуль чтения/записи (rd_wb_sel = 5).

- Первый регистр-операнд - x1 (rs1_addr = 1).

- Регистр-назначение - x5 (rd_addr = 5).

- Непосредственное значение - 32 (imm = 32).

Остальные поля не имеют значения для данной инструкций.

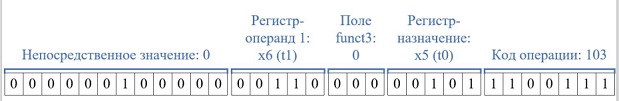

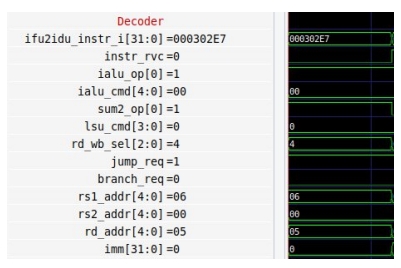

Декодирование инструкции (I-тип, jalr)

Рассмотрим декодирование инструкции безусловного ветвления (прыжка) I-типа на примере инструкции "jalr t0, t1". В данном случае смещение относительно адреса в t1 отсутствует, по этой причине imm = 0.

Инструкция в формате "hex": 0x000302E7.

- RVI инструкция (instr_rvc = 0).

- Вычисление адреса прыжка происходит без использования АЛУ, по данной причине ialu_cmd = 0.

- Операнды для вычисления адреса прыжка - значение в регистре t1 и непосредственное значение (sum2_op = 1).

- Источник данных для MPRF - инкрементированный счетчик инструкций (rd_wb_sel = 4).

- Поскольку инструкция выполняет прыжок jump_req = 1.

- Первый регистр-операнд - x6 (rs1_addr = 6).

- Регистр-назначение - x5 (rd_addr = 5).

- Непосредственное значение - 0 (imm = 0).

Остальные поля не имеют значения для данной инструкций.

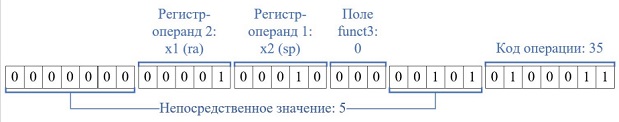

Декодирование инструкции (S-тип)

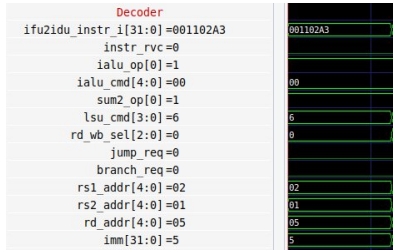

Рассмотрим декодирование инструкции записи S-типа на примере инструкции "sb ra, 5(sp)".

Инструкция в формате "hex": 0x001102A3.

- RVI инструкция (instr_rvc = 0).

- Вычисление адреса записи происходит без использования АЛУ, по данной причине ialu_cmd = 0.

- Операнды для вычисления адреса записи - значение в регистре sp и непосредственное значение (sum2_op = 1).

- Тип операции модуля чтения/записи - запись одного байта (lsu_cmd = 6)

- Запись в MPRF не осуществляется (rd_wb_sel = 0).

- Первый регистр-операнд - x2 (rs1_addr = 2).

- Второй регистр-операнд - x1 (rs1_addr = 1).

- Непосредственное значение - 5 (imm = 5).

Остальные поля не имеют значения для данной инструкций.