Полупроводниковая память ЭВМ

Память ЭВМ - это её функциональная часть, предназначенная для записи, хранения и выдачи данных.

Определим ряд терминов.

Запоминающее устройство (ЗУ) - устройство, физически реализующее функцию памяти данных и программ.

Обращение к ЗУ - это запись или считывание.

Быстродействие ЗУ - определяется продолжительностью операции обра-щения к ЗУ. Время обращения при записи определяется как

где  - время поиска числа;

- время поиска числа;

- время стирания ранее записанной информации (при необходимости);

- время стирания ранее записанной информации (при необходимости);

- время записи нового числа.

- время записи нового числа.

Время обращения при считывании рассчитывается как

где  - время собственно чтения;

- время собственно чтения;

- время восстановления считанных кодов (при необходимости).

- время восстановления считанных кодов (при необходимости).

ЗУ классифицируют:

-

по месторасположению по отношению к вычислительному устройству:

- внешние ЗУ;

- внутренние ЗУ;

-

по назначению:

- сверхоперативные (СОЗУ) - имеют быстродействие, соизме-римое с быстродействием вычислительного устройства. Служат для хранения ре-зультатов его промежуточных операций. В микропроцессорах (МП) роль СОЗУ выполняет рассмотренная выше регистровая память - встроенные в кристалл МП регистры общего назначения (РОНы).

- оперативные (ОЗУ) - энергозависимые ЗУ, служащие для пер-воначального сохранения вводимой информации. При потере питания информа-ция теряется;

- постоянные (ПЗУ) - энергонезависимое ЗУ, служащее для хранения неизменной информации (управляющих программ и программ, отла-женных пользователем);

- буферные (БЗУ) - предназначены для промежуточного хране-ния информации при её обмене между устройствами, работающими с разной ско-ростью. Эту роль выполняются регистровые схемы или ОЗУ малого объема;

- внешние (ВЗУ) - служат для хранения большого объёма ин-формации на внешнем по отношению к вычислительному устройству носителе, как правило, магнитном;

-

по физическим принципам действия:

- магнитные;

- полупроводниковые;

-

по способу хранения информации:

- статические;

- динамические;

-

по способу доступа к ячейке:

- с последовательным доступом - когда осуществ-ляется последовательное обращение к ячейкам до тех пор, пока не произойдет об-ращение к нужной ячейке с заданным адресом. Примером может служить накопи-тель на магнитной ленте;

- с циклическим доступом - когда из нужной ячей-ки информация считывается в определенные моменты, разделенные интервалом времени;

- с произвольным доступом.

Для получения в ЭВМ одновременно большой информационной ёмкости и высокого быстродействия используется так называемый иерархический принцип построения ЗУ (рис. 10.1), при котором логиче-ская организация потоков информации такова, что всё информационное поле ЭВМ или вычислительной системы представляется в виде внутреннего абстрактного виртуального ЗУ. Адресация его ячеек осуществляется посредством абстрактных математических адре-сов.

Далее рассматривается полупроводниковая память произвольного доступа.

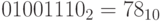

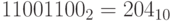

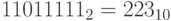

Информационная ёмкость (объём) памяти

Один разряд двоичного слова - 1 бит информации - сохраняется в элементарной ячейке памяти, называемой запоминающим элементом (ЗЭ). Для хранения информации, содержащейся в многоразрядном слове, необходима одно-мерная матрица памяти (рис. 10.2,а), в ко-торой разряды расставлены в соответствии со степенью числа 2. Разряд, соответствую-щий нулевой степени, называют младшим, максимальной - старшим. А для работы с большими массивами информации необходимы двумерные матрицы ЗЭ, имеющие задан-ную разрядность (ширину) и количество строк (длину). Так, на рис. 10.2,б показана матрица для хранения четырёх 8-разрядных чи-сел. Разрядность задают в битах или байтах (1 байт = 8 бит). Каждое число в память запи-сывается по определенному адресу, задаваемому опять-таки в двоичном коде. Так, на рис. 10.2,б, первое число (  ) имеет адрес

) имеет адрес  , следующее (

, следующее (  ) - адрес

) - адрес  , далее (

, далее (  ) -

) -  и последнее (

и последнее (  ) - адрес

) - адрес  . Таким образом, если n - разряд-ность адреса, то количество строк матрицы памяти будет равно

. Таким образом, если n - разряд-ность адреса, то количество строк матрицы памяти будет равно  . Информационный объём памяти обычно зада-ют в более крупных, нежели байт, единицах - в кило-, мега- и гигабайтах:

. Информационный объём памяти обычно зада-ют в более крупных, нежели байт, единицах - в кило-, мега- и гигабайтах:

Рис. 10.2. Информационный объём ЗУ: а - одномерная матрица для хранения одноразрядного числа; б - двумерная матрица на четыре 8-разрядных числа

Для организации матрицы памяти на кристалле каждой интегральной схемы ЗУ фор-мируются накопитель из ЗЭ и схемы обрамления.

Накопитель - это регулярная структура из отдельных ЗЭ.

Схемы обрамления - это совокупность схем, включающая в себя:

- дешифраторы выбора адресов ЗЭ;

- элементы управления режимами работы памяти (чтение, запись, хранение);

- формирователи сигналов, обеспечивающие сопряжение накопителя с внешними схемами.

Способы организации накопителей

Словарная организация

При работе накопителя данной организации (рис. 10.3,а) активный сигнал приходит только на одну адресную ли-нию. При этом происходит доступ ко всем запоминающим элементам выбранной строки. Иными словами, все двоичное число записывается или считывается одновременно.

Матричная организация

В данном типе накопителя (рис. 10.3,б) выбор ЗЭ происходит по двум адресным линиям. Одна линия условно называется линией выбора строки, а другая - линией выбора столбца. Активным становится тот запоминающий элемент в накопителе, у которого активны обе ад-ресные линии. Для работы с многоразрядными числами создаётся трехмерная матрица, на которую приходят те же линии адреса строки и столбца, но свои собственные разрядные линии. Для данного типа накопителя может быть использован ЗЭ на биполяр-ных многоэмиттерных транзисторах: один эмиттер соединяется с разрядной линией, а два остальных - к адресным линиям строки и столбца.