Этапы самостоятельного проектирования узла/устройства

Поведенческая верификация (отладка)

Поведенческая верификация предназначена для проверки соответствия разработанного RTL кода исходным алгоритмам и спецификациям. Процесс доработки кода в целях устранения ошибок в процессе верификации можно назвать отладкой работы устройства.

Отладка и поведенческая верификация демонстрационного примера выполнены в среде Quartus Prime. Для этого было сформировано тестовое окружение, которое представлено двумя файлами: файл структурного описания тестовой платформы для IP-блока, включающей в себя IP-блок и файл сценария тестирования. Тестовое окружение демонстрационного примера выполнено на языке VHDL.

В среде разработки кода (желательно, с синтаксическим расширением для выбранного языка разработки, в случае демонстрационного примера - HDL Designer) разрабатывается дополнительный тестирующий блок - Тестер, который подключается ко входам и выходам исследуемого модуля.

На выходе тестирующего блока формируются воздействия, соответствующие проверке каждого элемента сценария, таким образом генерируется файл описания тестовой платформы и файл сценария.

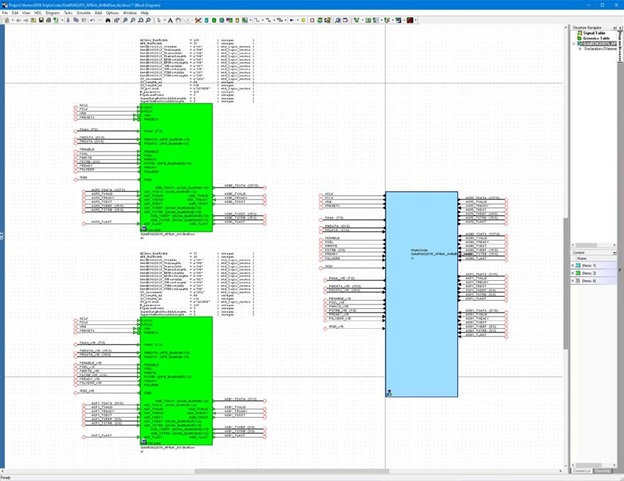

САПР позволяет работать в графическом режиме и формировать последовательность тестовых воздействий (рисунок 5.4).

При нажатии на блок появляется возможность в редакторе написать код или дополнить графическое описание процесса верификации (рисунок 5.5).

Для проверки работы модуля шифрования имеет смысл использовать тестовые воздействия, описанные в стандарте.

Для проверки работы обертки необходимо проверить все состояния машины состояний и все переходы между ними.

Пакет из файлов тестового окружения и исследуемого модуля загружаются в симулирующую программу, проводится запуск элементов сценария тестирования. Результат симуляции выводится на экран в виде временных диаграмм или в текстовый файл (см. рисунок 5.6).

Вопросы для самостоятельной работы

Выполняется самостоятельная работа по проектированию и поведенческой верификации устройства (можно взять уже готовые прототипы согласно индивидуальным вариантам или по пожеланию обучающегося). В результате выполнения этапа должен быть сформирован исходный код устройства по индивидуальному заданию, код обертки для подключения к соответствующему интерфейсу, заполнены основные разделы Спецификации.