Этапы самостоятельного проектирования узла/устройства

В результате выполнения этого этапа разработки формируются следующие материалы:

- спецификация (описание назначения, структурных элементов и параметров устройства на человеческом литературном языке);

- описание оборудования на языке HDL (описание структурных элементов устройства на языке описания оборудования - VHDL, Verilog, SystemVerilog);

- верификация поведенческая (создание тестовой платформы для подтверждения параметров, логики функционирования и особенностей оборудования).

При этом выполняется непосредственное проектирование алгоритмов работы узлов и описание этих алгоритмов на выбранном языке описания аппаратуры. Для демонстрационного примера приведена активность сигналов интерфейса (основные алгоритмы) при работе с интерфейсом APB, реализованная на языке VHDL.

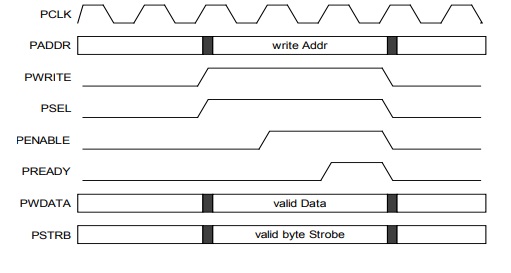

При записи служебной и управляющей информации используется интерфейс APB, позволяющий адресоваться к отдельным элементам хранения IP-блока. Одиночный цикл записи представлен на рисунке 5.1.

При правильном адресе обращения записаны будут только те байты, которые сопровождаются активным уровнем соответствующей линии PSTRB. К примеру, при записи двойного слова x"ABCDEF01" в сопровождении содержимого PSTRB = "1101" записаны будут только байты 3,2,0 (x"ABCD 01").

begin code example if (PSEL = '1' and PENABLE = '1' and PWRITE = '1' and PREADY_r = '1') then if (PADDR_r >= GstdR3432015_CtrAddr and PADDR_r < GstdR3432015_CtrAddr + GstdR3432015_CtrLength) then if (APB_BusWidth = 32) then for i in 0 to PSTRB'LENGTH-1 loop if (PSTRB(i) = '1') then GstdR3432015_Control_r((i*8)+7 downto i*8) <= PWDATA((i*8)+7 downto i*8); end if; end loop; -- i elsif (APB_BusWidth = 16) then… end code example

При ширине шины данных интерфейса APB в 8 бит - для записи двойного слова регистра управления потребуется четыре последовательных обращения по адресам соответствующих байтов регистра.

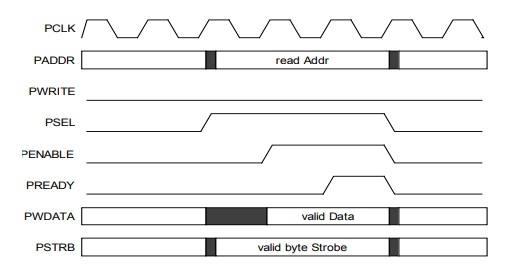

Одиночный цикл чтения представлен на рисунке 5.2.

При правильном адресе обращения на шину данных будут выданы только те байты, которые сопровождаются активным уровнем соответствующей линии PSTRB. К примеру, при чтении двойного слова в сопровождении содержимого PSTRB = "1011" реально прочитаны будут только байты 3,1,0. Позиции байтов, для которых PSTRB(i) = '0' - заполняются нулями. Т.е., прочитано будет двойное слово x"98005432".

При ширине шины данных интерфейса APB в 8 бит - для чтения двойного слова регистра состояния потребуется четыре последовательных обращения по адресам соответствующих байтов регистра.

begin code example if (PSEL = '1' and PENABLE = '1' and PWRITE = '0') then if (PADDR_r >= GstdR3432015_CtrAddr and PADDR_r < GstdR3432015_CtrAddr + GstdR3432015_CtrLength) then for i in 0 to PSTRB'LENGTH-1 loop if (APB_BusWidth = 32) then if (PSTRB(i) = '1') then PRDATA_r((i*8)+7 downto i*8) <= GstdR3432015_Control_r((i*8)+7 downto i*8); end if; elsif (APB_BusWidth = 16) then if (PADDR_r(1) = '0') then PRDATA_r((i*8)+7 downto i*8) <= GstdR3432015_Control_r((i*8)+7 downto i*8); else PRDATA_r((i*8)+7 downto i*8) <= GstdR3432015_Control_r(((i+2)*8)+7 downto (i+2)*8); end if; elsif (APB_BusWidth = 8) then… end code example

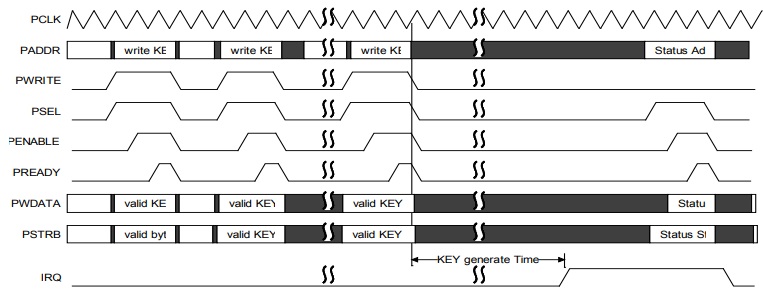

Активность интерфейса при загрузке ключа (KEY) или начального значения (IV) приведена на рисунке

После загрузки ключа или начального значения необходимо подождать выработки сигнала прерывания IRQ. Снятие сигнала IRQ обеспечивается чтением регистра состояния устройства. После этого устройство будет готово к приему пакетов данных по шине AXI Stream. Загрузка ключа и отработка прерывания представлены на рисунке 5.3.

При длине ключа в 256 бит и ширине шины данных APB в 32 бита потребуется 8 циклов записи для полной загрузки ключа в порт записи. По истечении времени генерации внутреннего ключа будет сформировано прерывание. После очистки флага прерывания чтением регистра состояния устройство готово к работе с новым ключом шифрования.

Начальное значение (IV) загружается таким же образом в порт загрузки IV.

Обертка для подключения к процессорному ядру реализована на языке VHDL, проект структурирован по отдельным файлам для улучшения условий отладки узлов и связности понимания логики работы. Полученный список файлов доработанного IP блока представлен в таблице 5.1.

| № | Файл | Тип | Описание |

|---|---|---|---|

| 1 | gstdr3432015_apbctr_ahbdflow_tb_struct.vhd | VHDL | Верхний уровень структуры IP-блока криптопреобразования информации |

| 2 | Kuznechik_GstdR34132015_MMv01_beha vior.vhd | VHDL | Модуль криптопреобразования, реализующий алгоритмы и режимы криптопреобразования в соответствии с ГОСТ Р 34.13-2015 |

| 3 | GstdR3432015_APBctr_AXIStrdflow_beha vior. vhd | VHDL | |

| 4 | FIFO_wyuxb_ryuxb_sclk_behavior.vhd | VHDL | Параметризуемый модуль FIFO, для организации временного хранения данных и команд интерфейса |