|

Здравствуйте! Прошел курс, а где экзамен? Как сертификат получить? Без экзамена? |

Комбинационные схемы

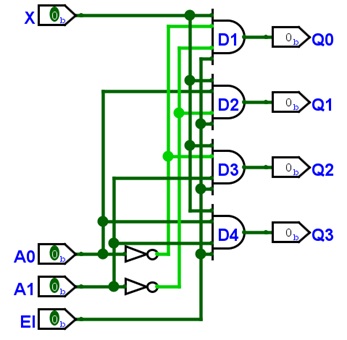

Обратной схемой для мультиплексора является демультиплексор. Демультиплексор - это функциональный узел, предназначенный для переключения сигнала с одного информационного входа на один из информационных выходов. На схемах обозначается (DX - ЕСКД), DMUX, DMX. На рисунке 2.9 приведена функциональная схема демультиплексора в среде Logisim Evolution.

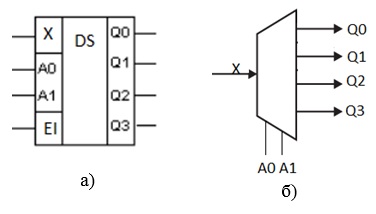

В таблице 2.4 приведена таблица работы данного узла. На рисунке 2.10а приедено УГО мультиплексора в системе ЕСКД, на 2.10б в системе ANSI.

| Адресные входы | Вход управления | Выходы | ||||

|---|---|---|---|---|---|---|

| A1 | A0 | E1 | Q0 | Q1 | Q2 | Q3 |

| X | X | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | X | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | X | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | X | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | X |

Если обратить внимание на таблицу работы и сравнить с таблицей истинности дешифратора, то можно обнаружить сходство в принципе работы. Поэтому если принять информационный вход Х= лог. "1", то демультиплексор начинает выполнять функцию дешифратора.

В среде Logisim Evolution, описанные выше элементы, за исключением шифратора (отсутствует) расположены во вкладке "Плексоры". В таблице 2.5 приведено условно-графическое обозначение данных, а также назначение сигналов.

| Наименование элемента (плексора) | Условно-графическое обозначение | Назначение сигналов |

|---|---|---|

| Мультиплексор |

1 - коммутируемые входы данных (шина данных); 2 - выходная линия (шина данных); 3 - шина адреса. |

|

| Демультиплексор |

1 - вход данных (шина данных); 2 -выходные линии (шины данных); 3 - шина адреса. |

|

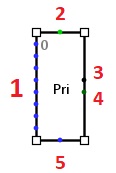

| Дешифратор (Декодер) |

1 - выходные линии; 2 - вход разрешения (по умолчанию активен); 3 - шина данных. |

|

| Шифратор приоритетов |

1- входные линии данных; 2 - выход разрешения для каскадирования, активен если на всех входных линиях 0 и работа шифратора разрешена; 3 - выход, содержащий адрес приоритетного бита; 4 - выход разрешения для каскадирования/ Выход активен если хотя бы на одном из входов присутствует 1 и работа шифратора разрешена; 5 - вход разрешения (по умолчанию активен); |

|

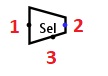

| Селектор битов |

1 - входная шина данных для выборки; 2 - выбираемый бит данных; 3 - селектор адреса выбираемого бита. Данная схема по функционалу схожа с мультиплексором для дискретных сигналов. |

Большинство из рассмотренных выше узлов будут применятся при организации сложных цифровых на основе схем с памятью и в арифметико-логическом устройстве проектируемого процессора.

В приложении 1 приведены коды описания аппаратуры для комбинационных схем, описанных в данном разделе.

Лабораторная работа 2. "Моделирование комбинационной схемы с применением инструмента комбинационного анализа"

Цель работы: получение практических навыков работы с инструментом комбинационного анализа таблиц истинности для построением схем в среде Logisim. Получение навыков разработки комбинационных схем - дешифраторов для индикации в среде Logisim и Intel Quratus PrimeLite.

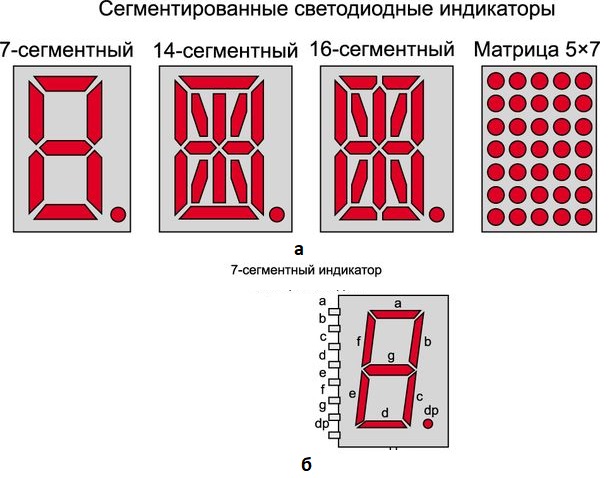

В цифровой микропроцессорной технике (системы управления оборудованием, измерительная техника) довольно часто можно встретить в качестве средств индикации не дисплеи, а символьные индикаторы в виде секций, например семисегментые индикаторы. Индикаторы бывают различного количества сегментов как следует из рисунка 2.12.а [3].

В качестве элементов, на которых реализуются индикаторы применяются светодиоды различных цветов. Каждому светодиоду отводится поименованная секция и соответствующий вывод (рисунок 2.2.б ). Для семисегментных индикаторов применяется поименованные буквами сегменты: a-g и точка, которая может обозначаться как h или dp.

В индикаторах светодиоды могут электрически объединяться в одну общую точку катод или анод. Индикаторы именуются с общим анодом (рисунок 2.12.а ) или общим катодом (рисунок 2.12.б )[5], что отражается в технической документации на данное изделие. Исходя из схем включения, различается и способ подачи сигналов на индикаторы. В качестве управляющих устройств может выступать постоянная память, программируемые логические матрицы или специальные дешифраторы. Проектирование как раз дешифратора осуществляется в данной работе.