Опубликован: 04.08.2025 | Доступ: свободный | Студентов: 12 / 0 | Длительность: 02:58:00

Лекция 6:

Разработка цифровых ИС на примере микроконтроллерного ядра SCR1 - топологическое проектирование

- PLATFORM - имя библиотеки;

- VERILOG_FILES - путь к исходным файлам;

- SDC_FILE - путь к фалу временных ограничений;

- CORE_UTILIZATION - процент использования кристалла стандартными ячейками;

- PLACE_DENSITY - плотность размещения ячеек (1 - плотно, 0 - разреженно)

- TNS_END_PERCENT - процент критических путей с отрицательными резервами, которые необходимо исправить (попытаться исправить).

- SKIP_CTS_REPAIR_TIMING - пропуск улучшения временных характеристик тактового дерева (для ускорения получения результатов).

- GPL_TIMING_DRIVEN - глобальное размещение с упором на временные характеристики (выключено для ускорения получения результатов).

- GPL_ROUTABILITY_DRIVEN - глобальное размещение с упором на упрощение трассировки (включено для ускорения получения результатов).

- REMOVE_ABC_BUFFERS - удаление буферов, вставленных при маппировании.

Топологическое проектирование - запуск маршрута

Для запуска маршрута необходимо в директории "scr1_top_axi" в "//flow" выполнить команду "make DESIGN_CONFIG=./designs/sky130hd/scr1_top_axi/config.mk". Опционально можно добавить строку "DESIGN_CONFIG=./designs/sky130hd/scr1_top_axi/config.mk" в файл "//flow/Makefile".

По окончании работы ПО необходимо выполнить команду "make gui_final DESIGN_CONFIG=./designs/sky130hd/scr1_top_axi/config.mk" (при добавлении "DESIGN_CONFIG" в Makefile нет необходимости его указывать при запуске gui). Данная команда запустит графический интерфейс.

Топологическое проектирование - анализ результатов

Перед рассмотрением результатов в графическом интерфейсе перечислим директории с результатами работы ПО:

- "//flow/results/sky130hd/scr1_top_axi/base" - выходные файлы ПО. Наиболее значимыми являются файлы топологии (6_final.def и 6_final.gds), физический Verilog-нетлист (6_final.v), файл временных ограничений (6_final.sdc) и файл паразитных параметров (6_final.spef).

- "//flow/reports/sky130hd/scr1_top_axi/base" - различные отчеты (результаты STA, анализа энергопотребления, DRC и т.д.)

- "//flow/logs/sky130hd/scr1_top_axi/base" - лог-файлы выполнения маршрута.

Топологическое проектирование - статический временной анализ

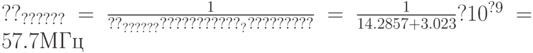

- В полученной топологии присутствует нарушение резерва установки (setup slack = - 3.023 нс).

- В файле временных ограничений необходимо уменьшить частоту тактового сигнала.

- Установим в файле временных ограничений период основного тактового сигнала 17.4 нс (~57.5 МГц).

- Нарушения резерва установки отсутствуют.

Нарушения резерва удержания (hold violations) отсутствуют:

Топологическое проектирование - статический временной анализ

- Другой способ борьбы с временными нарушениями - заставить ПО дополнительно оптимизировать критические пути.

- Воспользуемся командой "repair_timing -setup".

- Как можно видеть, резерв установки увеличился.

- Исправление резерва установки таким образом может вызвать ухудшение резерва удержания.

- Один из способов борьбы с нарушениями резерва удержания - задание на этапе логического синтеза неопределенности тактового сигнала "с запасом" и последующее его уменьшение.