Лекция 9: Мультиядерные процессоры на базе MIPS-совместимых ядер

Когерентная процессорная система MIPS32 1004K

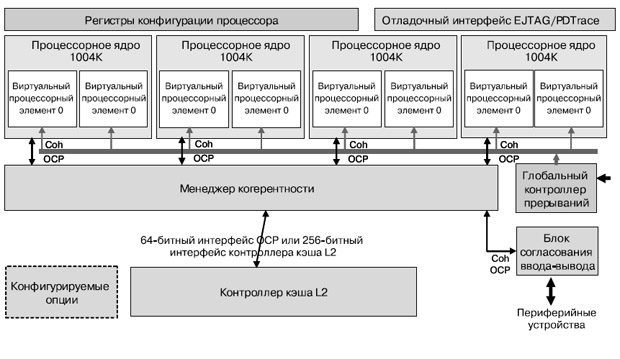

Наиболее близким конкурентом для мультиядерных ARM процессоров является когерентная процессорная система MIPS32 1004K, также содержащая до 4 процессорных ядер. Одним из существенных отличий системы MIPS32 1004K является поддержка ее процессорными ядрами двух потоков исполнения.

Когерентная процессорная система (CPS) MIPS32  1004K стала следующим шагом в развитии технологии процессоров от MIPS Technologies [52-53-54]. 1004K CPS является масштабируемой мультипроцессорной платформой, которая поддерживает до четырех ядер, подключенных с использованием когерентной архитектуры (

рис.

9.1). Каждое ядро системы аппаратно поддерживает несколько потоков. 1004K CPS оптимизирована для приложений типа "система-на-кристалле", обеспечивает высокую производительность благодаря снижению задержек доступа к памяти при помощи переключения потоков на время ожидания данных.

1004K стала следующим шагом в развитии технологии процессоров от MIPS Technologies [52-53-54]. 1004K CPS является масштабируемой мультипроцессорной платформой, которая поддерживает до четырех ядер, подключенных с использованием когерентной архитектуры (

рис.

9.1). Каждое ядро системы аппаратно поддерживает несколько потоков. 1004K CPS оптимизирована для приложений типа "система-на-кристалле", обеспечивает высокую производительность благодаря снижению задержек доступа к памяти при помощи переключения потоков на время ожидания данных.

Когерентная мультипроцессорная система применяет многопоточность для увеличения производительности по сравнению с традиционными мультипроцессорными системами. Система поддерживает до четырех процессорных ядер с аппаратной поддержкой двух потоков в каждом ядре. Многопоточность дополняется многоядерностью — как следствие, есть возможность поддерживать SMP-операционные системы и модели программирования с минимальными аппаратными затратами. Основные области применения:

- "цифровой дом";

- телекоммуникационные приложения;

- автомобильные информационные системы;

- средства автоматизации офиса (многофункциональные офисные устройства).

Аппаратная поддержка когерентности снижает программные издержки.

Основные возможности когерентной мультипроцессорной системы MIPS32  1004K

1004K  :

:

- от 1 до 4 1004K многопоточных ядер (в совокупности до 8 аппарат-но поддерживаемых потоков);

- блок управления согласованием (CM) — управление согласованием ядер и ввода-вывода;

- блок согласования ввода-вывода — аппаратный блок для согласования нагрузки ввода-вывода между программной реализацией и процессорными ядрами;

- глобальный контроллер прерываний (GIC) — системный и межъядерный контроллер прерываний;

- расширенный 256-битный интерфейс к контроллеру кэша второго уровня;

- блок отладки и трассировки EJTAG/PDtrace

.

.

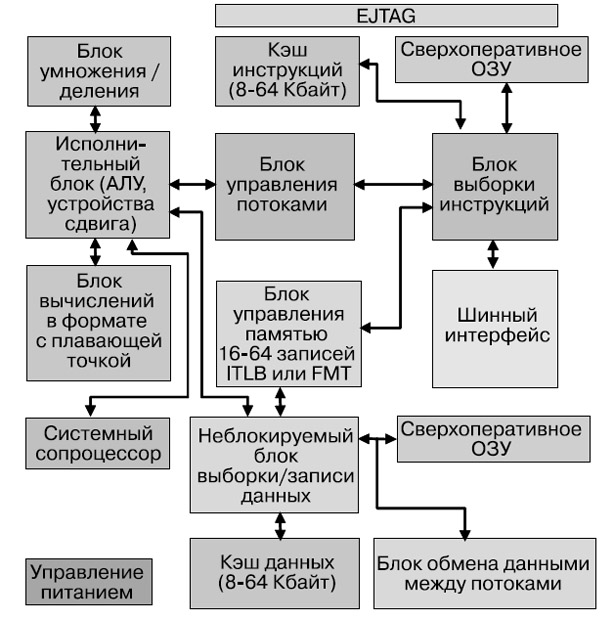

Базовое ядро системы [54] ( рис. 9.2) 1004K имеет 9-уровневый конвейер, благодаря которому производительность системы составляет более 1,5 DMIPS/МГц на ядро. Каждое ядро поддерживает операции с одним или двумя аппаратными потоками.

Для реализации аппаратной поддержки нескольких потоков используются виртуальные процессорные элементы (Virtual Processing Elements — VPEs). Существуют две версии ядер — с поддержкой операций с плавающей точкой (1004Kf) и без (1004Kc). Ядра поддерживают MIPS32 DSP ASE версии 1. Согласованные порты имеют дублированные теги кэша для фоновой проверки когерентности. Предусмотрена конфигурация таблиц данных и инструкций TLB, кэшей, буферного ОЗУ и некоторых других опций на этапе создания.

Система на кристалле XLP832

Процессор является масштабируемой системой на кристалле, которая включает ключевые функции коммуникационных систем, в том числе безопасность проводных и беспроводных систем, сетевые приложения, системы хранения данных, системы балансировки нагрузки и другие приложения. XLP Processor  стал третьим поколением усовершенствований многопоточной, мультиядерной архитектуры семейства XLR

стал третьим поколением усовершенствований многопоточной, мультиядерной архитектуры семейства XLR  Processor [55,56].

Processor [55,56].

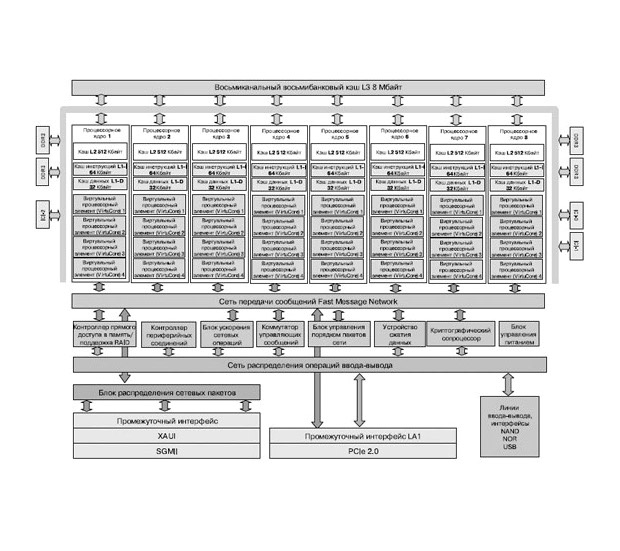

Процессор XLP832 (

рис.

9.3) создан по 40-нм технологическому процессу. Ядра работают в диапазоне частот от 500 Гц до 2 ГГц, что в итоге дает более чем трехкратный прирост производительности в пересчете на Ватт по сравнению с процессорами серии XLR. Процессоры серии XLP832 обратно совместимы по программному обеспечению с процессорами серий XLR и XLS  [56].

[56].

Каждое из восьми ядер, составляющих процессор, одинаково хорошо подходит как для задач обработки данных, так и для задач управления. Для поддержания высокой производительности при поточной обработке данных архитектура ядер EC4400 поддерживает несколько потоков на аппаратном уровне, ядра также поддерживают суперскалярный режим с внеочередным исполнением команд. Сочетание планирования четырех инструкций и поддержки четырех последовательных потоков создает "систему на кристалле" с высокой производительностью. Каждый из четырех потоков, поддерживаемых ядром, представляется программному обеспечению как отдельный процессорный элемент (VirtuCores  ), что существенно упрощает разработку программного обеспечения и увеличивает общую производительность системы.

), что существенно упрощает разработку программного обеспечения и увеличивает общую производительность системы.

Ядро EC4400 представляет собой MIPS64 Release-II ISA-совместимый процессор, с поддержкой виртуальной памяти. Содержит IEEE754- и MIPS-совместимый блок арифметики в формате с плавающей точкой. Рабочие частоты — от 500 МГц до 2 ГГц. Процессор XLP имеет прирост производительности в расчете на Ватт более чем в три раза по сравнению с серией XLR.

Процессор имеет согласованный трехуровневый кэш архитектуры MOESI+. Ключевые особенности следующие.

Высокоскоростная сеть передачи сообщений (FMN) с малым временем отклика позволяет взаимодействовать виртуальным ядрам (VirtuCores), устройствам и вводу-выводу. Сеть FMN позволяет обмениваться блокам сообщений без блокировок и семафоров. Передавая контрольные сообщения (дескрипторы), FMN предусматривает последовательный доступ без блокировок к периферийным устройствам, причем простым и прозрачным образом, что увеличивает в результате производительность драйверов устройств.

Процессор имеет несколько автономных специализированных ускорителей, которые снимают часть нагрузки с вычислительных ядер, оставляя им вычислительные задачи.

Три встроенных интерфейса согласования (ICI) могут объединять до четырех процессоров XLP832. Пропускная способность каждого интерфейса 80 Гб/с (полный дуплекс). Интерфейсы программно полностью прозрачны. Аппаратно поддерживается согласованность данных, передача сообщений между потоками, разделение памяти и ресурсов ввода-вывода.

Многоскоростные последовательные интерфейсы SERDES поддерживают следующие комбинации;

Сетевой ускоритель поддерживает обработку потока пакетов в 40 Гб/с. Возможности модуля включают в себя: программируемый анализ пакетов, вычисление и проверка контрольных сумм в форматах FCoE, iSCSI, SCTP; вычисление контрольных сумм входящих/исходящих пакетов TCP/UDP/IP; сегментацию TCP-трафика; поддержку протокола IEEE1588v2.

Устройство упорядочивания пакетов (POE) поддерживает упорядочивание пакетов размером вплоть до 64 Кбайт. Производительность POE составляет до 60 миллионов пакетов в секунду, то есть 40 Гб/с при 64-байтных пакетах.

Криптографический модуль с пропускной способностью 40 Гб/с:

- 10 криптографических ядер;

- поддержка алгоритмов DES/3DES, AES (128, 192, 256), ARC4/RC4; MD5, SHA-1, SHA-256/384/512 и SNOW3G (All HMAC), DES/3DES, AES (128, 192, 256), ARC4/RC4, RSA/DH. Показатели для протокола SSL/IPSec — до 30,000 RSA-обменов ключами в секунду (60,000 CRT), ECC (Elliptic Curve Cryptography).

Модуль сжатия/декомпрессии данных — 10 Гб/с.

8-канальный блок прямого доступа в память и блок хранения данных:

- поддержка RAID-5 XOR;

- вычисления RAID-6 P+Q Galois;

- поддержка поиска и ликвидации дублирующих данных.

Система имеет четыре контроллера PCIe 2.0, два USB-порта, режимы хоста и клиента, интерфейс PCMCIA, интерфейсы к NAND и NOR флэш-памяти, два KC-интерфейса, два асинхронных интерфейса 16550 UART, линии ввода-вывода. Также поддерживаются динамическое управление частотой каждого ядра, динамическое управление напряжением питания, статический выбор частоты для критических блоков (bridges, interconnects, DMA, etc.).

Краткие итоги

Описанные в лекции процессоры, кроме параллелизма, присущего мультиядерным системам, применяют параллелизм на уровне потоков, что позволяет более эффективно использовать пропусную способность подсистемы памяти и вычислительные ресурсы процессорного ядра, минимизируя простои, связанные с ожиданием окончания операций обмена с памятью.

Контрольные вопросы

- Почему мультипроцессорная система MIPS32 1004K называется когерентной?

- Опишите структуру ядра 1004K.

- Опишите структуру процессора XLP832

- Каковы основные характеристики ядра EC4400?