Лекция 3: Высокопроизводительные многоядерные процессоры для встраиваемых приложений

"Ячеистые" процессоры компании Tilera

Процессоры Tile-64/64Pro

Процессоры Tile64[7-8-9] рассчитаны на применение в высокопроизводительном сетевом оборудовании, беспроводных телекоммуникационных системах, а также серверах для потоковой обработки видеоданных. Позволяют использовать во встраиваемых приложениях мощные вычислительные ресурсы при достаточно низких энергозатратах.

Круг целевых задач для данных процессоров следующий.

Процессоры способны работать в сетях с уровнем трафика порядка 10-20 Гб/с, обеспечивая поддержку следующих сервисов:

- обнаружение/предотвращение вторжений (IDS/IPS);

- общее управление рисками (UTM);

- анализ пакетов 4-7 уровней;

- мониторинг сети;

- планирование качества обслуживания (QoS).

Мультимедиа-приложения, прежде всего включают цифровую обработку данных, легко замещая несколько цифровых сигнальных процессоров (ЦПС) или FPGA:

- кодирование/декодирование видео;

- потоковое и IP-видео (IPTV);

- диагностика проблем;

- пост-обработка видеоданных.

Применение в области беспроводных коммуникаций включает работу в существующих сетях GSM/CDMA и в сетях следующего поколения WiMAX & LTE. Прежде всего, это:

- базовые приемо-передающие станции (BTS);

- контроллеры базовых станций (BSC);

- шлюзы кампусной зоны (GGSN, SGSN, media gateway).

Процессор Tile64 может быть оптимизирован для выполнения определенных задач. Теоретически Tile64 будет обеспечивать десятикратный прирост производительности по сравнению с серверным процессором Intel Xeon при значительно меньшем энергопотреблении.

Tile64Pro является процессором общего назначения с MIMD-архитектурой. Каждое ядро может работать и под управлением собственной операционной системы, и под управлением многопроцессорной системы типа SMP Linux, соответственно, одновременно процессор может поддерживать различные приложения, к примеру, обработку видеокадров, шифрование данных и обработку стека сетевых протоколов.

Виртуальная память и технология Tilera's Multicore Hardwall позволяет осуществлять защиту данных на уровне ядра, как для общей памяти, так и для потоков и сообщений пользовательского уровня.

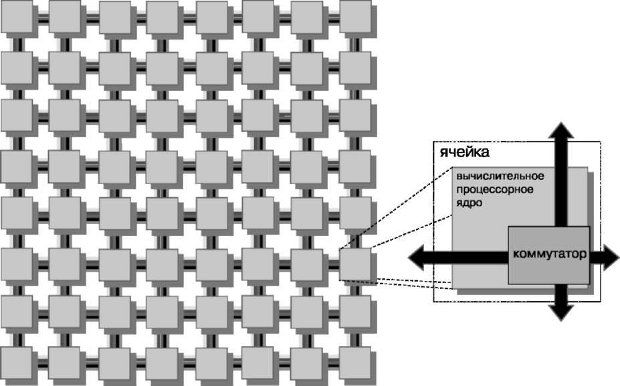

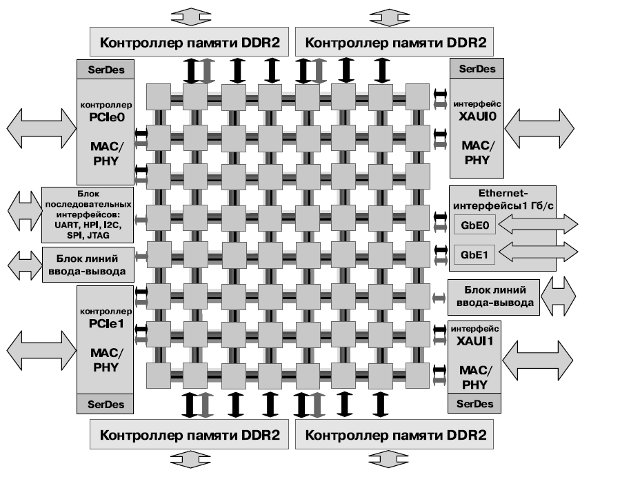

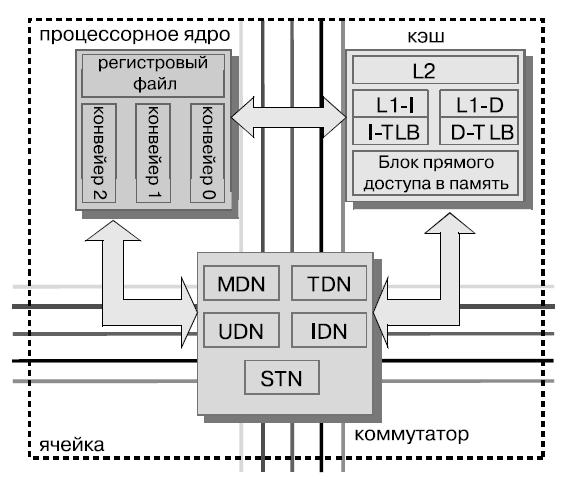

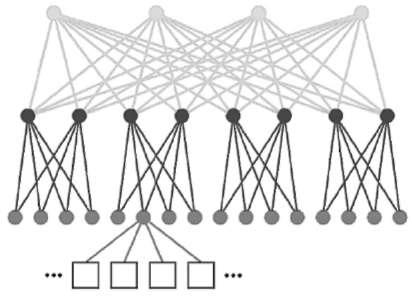

Процессор содержит 64 идентичных вычислительных ячейки (tile), организованных в двумерный массив 8х8 ( рис. 3.1) [8]. Ячейка является базовым блоком процессора и состоит из комбинации коммутатора и RISC-ядра общего назначения. Каждое ядро представляет собой полноценный RISC-процессор, работающий на частотах от 600 МГц до 1 ГГц, и содержит кэши первого и второго уровней (L1, L2 cache).

Ядро имеет все основные возможности обычного процессора, такие как:

- полный доступ к памяти и портам ввода-вывода;

- виртуальная память и защита данных (MMU/TLB);

- иерархический кэш с отдельными уровнями L1-I и L1-D;

- многоуровневая система прерываний;

- трехканальный конвейер VLIW, позволяющий выбирать 3 инструкции за цикл.

Каждое из ядер процессора Tile64 имеет собственную кэш-память первого и второго уровней ( рис. 3.2). При необходимости кэши L1 и L2 могут быть объединены для формирования общего кэша суммарным объемом в 5 Мб ( рис. 3.3). Процессоры семейства TilePro поддерживают технологию когерентного кэша Tilera's DDC (Dynamic Distributed Cache) — динамический распределенный когерентный кэш, обеспечивающий в два раза большую производительность по сравнению с обычными многоядерными процессорами.

Ядра оптимизированы для обеспечения наивысшей производительности при минимальном потреблении энергии. При работах на частотах между 500 и 1000 МГц энергопотребление составляет 170-300 мВт в расчете на ядро для типичных приложений. Соответственно, суммарное энергопотребление процессора составляет около 20 Вт.

Распределенный по ядрам когерентный кэш обеспечивает малое время задержки и большую емкость. Подсистема кэша состоит из высокопроизводительной двухуровневой неблокирующей иерархии кэшей. Двухуровневое решение изолирует кэш первого уровня (L1-инструкций и L1-данных) от лишних операций обращения к памяти, сохраняя решение быстрым и энергоэффективным. Аппаратная предварительная выборка инструкций для кэша инструкций L1-I уменьшает частоту промахов кэша. Программируемый блок прямого доступа в память позволяет осуществлять объемные передачи данных. Архитектура процессора разработана таким образом, что отдельному ядру доступен распределенный по другим ядрам кэш. Такая организация когерентного кэша предусматривает аппаратный контроль за доступом к общей распределенной памяти, это и позволяет ядру иметь доступ к набору локальных кэшей всех остальных ядер, работая как кэш третьего уровня.

Организованный данным образом кэш устраняет узкое место при доступе в глобальную внешнюю память — снижает частоту обращений.

Система когерентности кэшей позволяет получить доступ к странице памяти, кэшированной одним из ядер, и к остальным ядрам процессора при помощи операций чтения/записи (аналогично обращению к собственному кэшу ядра). Фактически ядро, кэшируя данные для себя, кэширует их для всех остальных ядер, независимо от их потребности в этих данных, что повышает производительность процессора в целом.

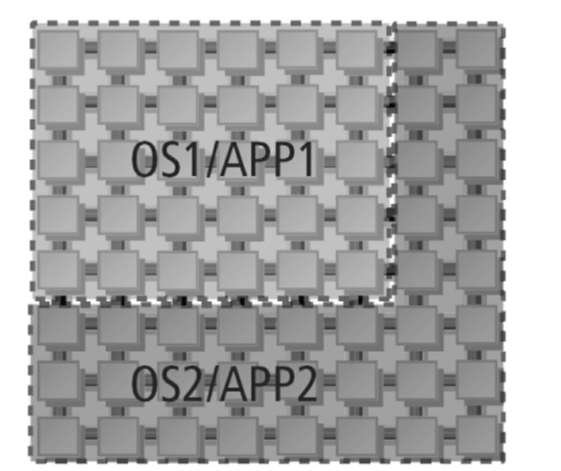

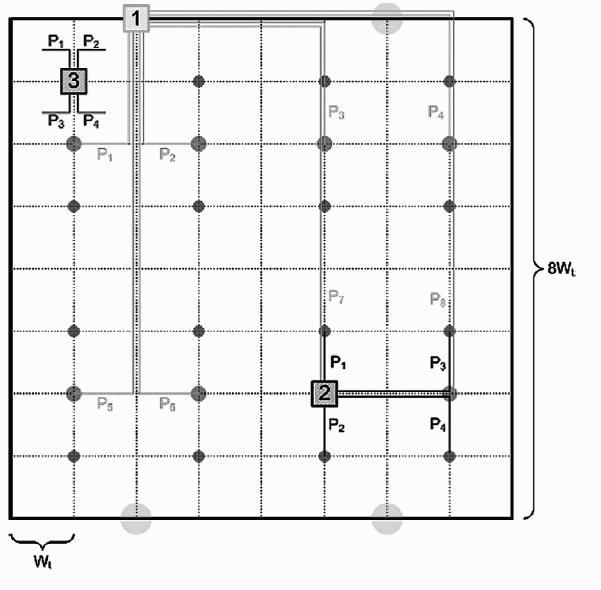

Технология Multicore Hardwall позволяет пользователю выделить одно или несколько ядер в относительно независимую процессорную группу, исключая коммуникации между выделенной группой и остальными ядрами, не включенными в группу. Если пакет данных пересекает установленную границу группы, вызывается прерывание и управление передается гипервизору — небольшой программе исполнительного уровня для отслеживания и управления системными ресурсами. Это обеспечивает защиту данных приложения в многозадачной среде. Технология Multicore Hardwall защищает множественные приложения и операционные системы от непредвиденных взаимодействий и случайных ошибок ( рис. 3.4).

Сеть iMesh обеспечивает высокоскоростную передачу данных, необходимую для устранения узкого места системы и поддержки масштабирования приложений. iMesh состоит из пяти отдельных подсетей. Две подсети управляются полностью аппаратно и используются для передачи данных между ядрами и памятью при промахах кэша или при прямом доступе в память. Три оставшиеся подсети доступны для приложений, позволяют осуществлять взаимодействие между ядрами и между ядрами и устройствами ввода-вывода. Для доступа к аппаратуре используется некоторое количество абстракций, например, потоковые каналы, аналогичные сокетам, или интерфейс передачи сообщений. Сеть iMesh позволяет передавать данные без остановки приложений, выполняющихся на ядрах. Это позволяет осуществлять обмен данными между ядрами и осуществлять контроль и маршрутизацию для каждого сетевого соединения, включая буферизацию и контроль потока по всей сети ( рис. 3.5).

Коммутатор, расположенный возле ядра, является неблокируемым и

подключает ядро к внутрикристальной сети Tilera's iMesh  , которая позволяет каждому отдельному ядру взаимодействовать с находящимися поблизости

ядрами. Скорость передачи данных по сети iMesh может достигать 27 Тбит/с.

, которая позволяет каждому отдельному ядру взаимодействовать с находящимися поблизости

ядрами. Скорость передачи данных по сети iMesh может достигать 27 Тбит/с.

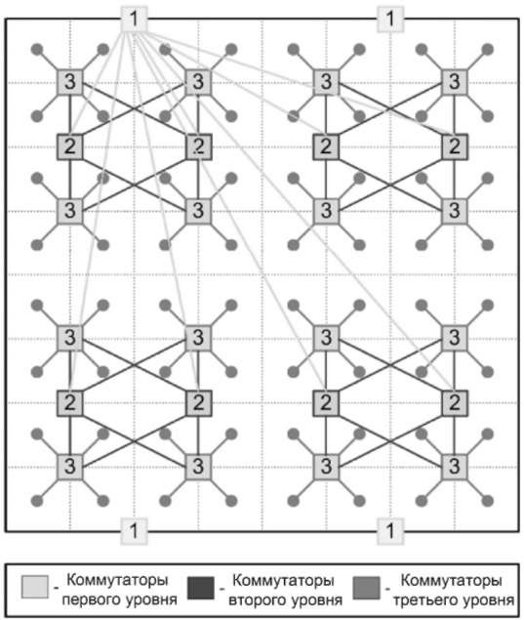

Сеть реализована по топологии "толстого дерева" (Fat Tree) ( рис. 3.6, рис. 3.7) [11,12].

Средства разработки включают в себя среду Tilera's Multicore

Development Environment  (MDE), имеющую в своем составе стандартные

средства параллельного программирования для многоядерных систем.

(MDE), имеющую в своем составе стандартные

средства параллельного программирования для многоядерных систем.

Среда Tilera's MDE содержит:

- стандартную интегрированную среду разработки, основанную на Eclipse;

- компилятор ANSI C/C++;

- симулятор;

- систему отладки и анализа производительности;

- широкие возможности интерфейса командной строки;

- полную поддержку системы SMP Linux;

- библиотеку iLib для повышения эффективности межъядерных коммуникаций;

- отладочные платы PCIe.

Библиотека iLib предоставляет программные интерфейсы, которые позволяют разработчикам:

- масштабировать прикладные программы от одного ядра до множества ядер;

- абстрагировать межъядерную передачу данных в виде потоков или передач сообщений;

- эффективно управлять ресурсами процессора.