|

Здравствуйте Владимир (Ефименко). Я обучаюсь по программе повышения квалификации "Наноэлектронная элементная база информатики на основе полупроводников и ферромагнетиков". У меня проблема с тестом № 2 (к лекции № 2) по этой программе. Я несколько раз пытался пройти этот тест, но больше 50 баллов набрать не удаётся, хотя я всё делаю в соответствии сматериалом лекции. В заданиях этого теста есть ошибки, которые видны невооружённым глазом. Обращаюсь к Вам как к инспектору этой программы повышения квалификации. Найдите возможность исправить ошибки в тесте № 2. Из-за остановки на этом тесте я не могу двигаться дальше, а у меня очень ограниченное время на освоение этой программы. Заранее благодарен Вам за внимание к моим проблемам и помощь. |

Наноэлектронные устройства памяти на кремниевых КМДП транзисторах

Введение

С использованием наноэлектронной кремниевой КМДП технологии строят не только сложные логические схемы, процессоры и высококлассные цветные фоточувствительные матрицы, описанные в предыдущей лекции, но и разнообразные интегральные устройства памяти. Принципы построения основных вариантов такой памяти мы и рассмотрим в данной лекции.

"Статическая" оперативная память с произвольным доступом

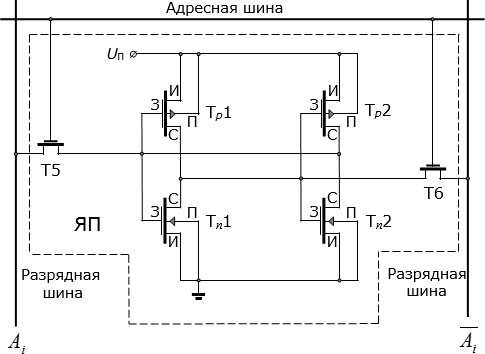

Сам по себе МДП транзистор не имеет памяти. Поэтому "чистую" память на КМДП транзисторах (т.е. без использования дополнительных элементов) можно построить лишь на триггерах, каждый из которых состоит из двух КМДП инверторов, описанных в п. 5.2.1. Принципиальная электрическая схема одной ячейки такой памяти показана на

рис.

6.1. Выход первого инвертора, состоящего из  -канального транзистора

-канального транзистора  и

и  -канального транзистора

-канального транзистора  , присоединен ко входу второго инвертора, состоящего из транзисторов

, присоединен ко входу второго инвертора, состоящего из транзисторов  и

и  . А выход второго инвертора присоединен ко входу первого. Благодаря такой перекрестной обратной связи и получается бистабильная схема триггера.

. А выход второго инвертора присоединен ко входу первого. Благодаря такой перекрестной обратной связи и получается бистабильная схема триггера.

Когда на затворах транзисторов первого инвертора потенциал низкий, транзистор  открыт, транзистор

открыт, транзистор  закрыт, и на выходе этого инвертора устанавливается высокий потенциал, близкий к потенциалу источника питания

закрыт, и на выходе этого инвертора устанавливается высокий потенциал, близкий к потенциалу источника питания  . Поскольку этот выход электрически соединен с затворами транзисторов второго инвертора, то транзистор

. Поскольку этот выход электрически соединен с затворами транзисторов второго инвертора, то транзистор  открыт, а транзистор

открыт, а транзистор  закрыт. На выходе второго инвертора устанавливается низкий потенциал, который и поддерживает первое стабильное состояние триггера.

закрыт. На выходе второго инвертора устанавливается низкий потенциал, который и поддерживает первое стабильное состояние триггера.

Рис. 6.1. Принципиальная электрическая схема ячейки памяти (ЯП) "статического" ОЗУ на триггере из КМДП транзисторов и подключения ее к адресной и разрядным шинам

Когда на затворах первого инвертора потенциал высокий, транзистор  закрыт, транзистор

закрыт, транзистор  открыт, и на выходе этого инвертора устанавливается низкий потенциал, близкий к потенциалу "земли". Поэтому транзистор

открыт, и на выходе этого инвертора устанавливается низкий потенциал, близкий к потенциалу "земли". Поэтому транзистор  закрыт, а транзистор

закрыт, а транзистор  открыт. На выходе второго инвертора устанавливается высокий потенциал, который и поддерживает альтернативное стабильное состояние триггера. Триггер – это классический бистабильный элемент, который сохраняет 1 бит информации.

открыт. На выходе второго инвертора устанавливается высокий потенциал, который и поддерживает альтернативное стабильное состояние триггера. Триггер – это классический бистабильный элемент, который сохраняет 1 бит информации.

Для того, чтобы каждый триггер, из которых состоит память, имел индивидуальный адресный доступ, в состав ячейки вводят также 2 ключевых МДП транзистора – Т5 и Т6.

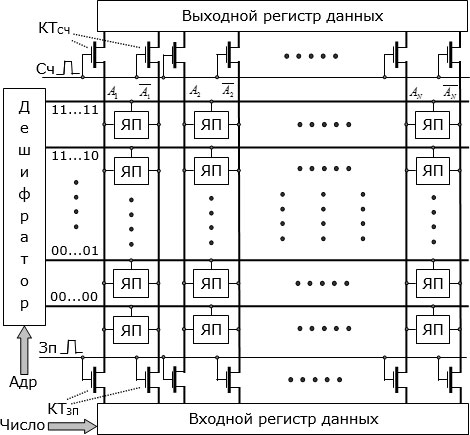

Ячейки памяти (ЯП) располагают в виде матрицы (

рис.

6.2). На одном из уровней межсоединений формируют систему горизонтальных, на другом – систему вертикальных металлических шин. Горизонтальные шины – адресные. Возле каждой из них на

рис.

6.2 указан соответствующий двоичный адрес. В каждом такте считывания или записи высокий потенциал подают от дешифратора лишь на одну из них, соответствующую заданному коду адреса (Адр). Все другие находятся под потенциалом "земли". Поэтому лишь в выбранной строке матрицы ключевые транзисторы (Т5 и Т6 на

рис.

6.1) открываются. Во всех других строках они закрыты. Вертикальные шины называют "разрядными". Каждый разряд представлен двумя шинами ( и

и  ).

).

При считывании потенциалы на этих шинах определяются состоянием соответствующего триггера в выбранной строке, так как во всех других строках ключевые транзисторы (Т5 и Т6) закрыты.

Рис. 6.2. Структурная схема узла "статического" оперативного запоминающего устройства с произвольным доступом (ОЗУ) на КМДП транзисторах

Например, если в триггере сохраняется логический "0", то  = 0 (потенциал низкий),

= 0 (потенциал низкий),  = 1 (потенциал высокий); если же сохраняется логическая "1", то

= 1 (потенциал высокий); если же сохраняется логическая "1", то  = 1,

= 1,  = 0. В режиме считывания на шину Сч подают положительный импульс напряжения. Это напряжение, приложенное к затворам ключевых транзисторов считывания КТСЧ, открывает их. Из разрядных шин потенциалы передаются в выходной регистр данных. Параллельно (т.е. одновременно) может считываться содержимое всех N разрядов матрицы памяти.

= 0. В режиме считывания на шину Сч подают положительный импульс напряжения. Это напряжение, приложенное к затворам ключевых транзисторов считывания КТСЧ, открывает их. Из разрядных шин потенциалы передаются в выходной регистр данных. Параллельно (т.е. одновременно) может считываться содержимое всех N разрядов матрицы памяти.

Для записи новых данных во входной регистр данных заносят двоичное число, которое должно быть записано по указанному адресу, и через шину записи (Зп) подают на затворы ключевых транзисторов записи КТЗП положительный импульс напряжения. Эти транзисторы открываются и присоединяют разрядные шины матрицы памяти к выходам входного регистра данных. Электрические потенциалы, которые действуют на этих выходах, принудительно переключают триггеры выбранной строки в соответствующее состояние, которое запоминается и сохраняется после окончания импульса записи. На триггеры других строк эти потенциалы не влияют, так как ключевые транзисторы (Т5 и Т6) в тех строках закрыты.

В режиме хранения ключевые транзисторы КТСЧ и КТЗП закрыты, на всех выходах дешифратора действует низкий потенциал, из-за чего во всех строках матрицы памяти ключевые транзисторы (Т5 и Т6 на рис. 6.1) также закрыты. Все ячейки памяти (ЯП) находятся в статическом режиме и практически не расходуют электроэнергию. Заметное потребление электрического тока и выделение тепла имеют место лишь во время перезаписи информации, когда приходится перезаряжать соответствующие паразитные емкости. Чем меньше размеры ячеек памяти и разрядных шин, тем меньше по величине эти паразитные емкости, и тем меньше выделение тепла. Скорость считывания данных и записи новой информации может быть как очень низкой, так и очень высокой – такой же, как и скорость переключения КМДП логических схем. При ПТН 32 нм максимальная скорость может достигать порядка 1 ГГц. Когда перезапись данных происходит редко, тогда выделение тепла мало. Доступ к данным в такой памяти – произвольный, адресный.

Записанная в триггеры информация сохраняется до тех пор, пока они подключены к источнику питания UП. Если питание (даже на короткое время) выключается, то записанная информация пропадает. Поэтому описанная статическая память не является энергонезависимой.

Другим недостатком такой памяти является то, что для адресной записи, хранения и считывания каждого бита информации требуется аж 6 МДП транзисторов. При проектно-технологической норме 32 нм одна ячейка памяти занимает на пластине кремния площадь приблизительно  , поэтому плотность хранения информации составляет приблизительно 5 Мбит/мм2. Для нанотехнологии это – сравнительно низкий показатель.

, поэтому плотность хранения информации составляет приблизительно 5 Мбит/мм2. Для нанотехнологии это – сравнительно низкий показатель.

Описанную быструю оперативную память широко применяют в составе микропроцессоров, микроконтроллеров, микроконверторов для реализации регистров и встроенной кэш-памяти, сверхбыстрых узлов оперативной памяти, – везде, где нужны произвольный доступ и высокая скорость считывания/записи данных при не очень большом их объеме.

В англоязычных источниках описанную оперативную КМДП память с произвольным доступом обычно называют "статической памятью" – "SRAM" (Static Random Access Memory) в отличие от "динамической памяти", которую мы рассмотрим в следующем пункте.