|

приветствую создателей курса и благодарю за доступ к информации! понимаю, что это уже никто не исправит, но, возможно, будут следующие версии и было бы неплохо дать расшифровку сокращений имен регистров итд, дабы закрепить понимание их роли в общем процессе. |

Прерывания и особые случаи

Контроллер приоритетных прерываний

Прерывание - один из наиболее дефицитных ресурсов в микропроцессорной системе. Микропроцессор имеет только 2 входа для приема запросов прерываний: вход INT - по нему принимаются запросы, обработка которых может быть замаскирована сбросом флага IF в регистре флагов, - и вход немаскируемых прерываний NMI. Вход NMI фактически закреплен за запросами прерываний от схем контроля питания. Поэтому при такой архитектуре микропроцессора в микропроцессорной системе обязательно должны использоваться средства, которые позволяют предварительно обрабатывать и передавать на вход маскируемых прерываний INT микропроцессора запросы от многочисленных внешних устройств, входящих в состав микропроцессорной системы. В качестве такой схемы используется контроллер приоритетных прерываний (КПП).

Мы рассмотрим его функционирование на примере БИС i8259, которая, с одной стороны, имеет самостоятельное значение, а с другой стороны, фактически без изменений входит в состав современных чипсетов.

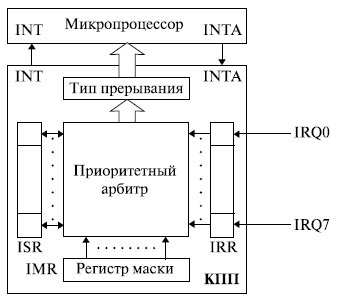

Его структура представлена на рис. 7.5.

Функции контроллера приоритетных прерываний:

- восприятие и фиксация до 8 запросов прерываний (IRQ0 - IRQ7), поступающих по внешним входам;

- выделение наиболее приоритетного из поступивших запросов, включая возможность маскирования отдельных запросов;

- выдача на шину данных (по требованию микропроцессора) типа выбранного прерывания.

При использовании КПП обработка запросов немаскируемых прерывание проходит следующие этапы:

- Системная периферия на системной плате или устройство ввода/вывода на внешней шине активирует одну из линий IRQx.

- В регистре запросов прерываний IRR, который предварительно настраивается на восприятие запросов по спаду или низкому уровню сигнала, происходит установка соответствующих разрядов в "1".

- Незамаскированные в регистре маски IMR запросы передаются в приоритетный арбитр, замаскированные блокируются.

- В соответствии с выбранной в процессе инициализации дисциплиной обслуживания приоритетный арбитр выделяет наиболее приоритетный запрос. При системном сбросе контроллера самый высокий приоритет устанавливается для запроса, приходящего по входу IRQ0, а самый низкий - по входу IRQ7.

- Приоритет выделенного запроса сравнивается с приоритетом запроса, который в данный момент может обрабатываться микропроцессором (его номер установлен в регистре обслуживания прерываний ISR ). Если приоритет нового запроса выше либо в данный момент обслуживаемых запросов нет, то контроллер формирует сигнал прерывания INT в микропроцессор, в противном случае обработка запроса откладывается. В регистре типа прерывания формируется тип принятого к обработке запроса прерывания.

- МП воспринимает запрос прерывания, и если флаг IF = 1, то по завершении текущей команды выполняет 2 цикла подтверждения прерывания, выдавая сигналы на выход INTA:

- МП принимает тип прерывания и использует его в качестве индекса при обращении к соответствующей таблице прерываний ( таблице векторов или таблице дескрипторов прерываний в зависимости от режима работы МП).

- В соответствии с установленным в микропроцессоре режимом работы (реальном или защищенном) и механизмом вызова программы - обработчика прерывания МП сохраняет необходимую информацию о прерываемой программе и переходит к выполнению обработчика прерывания.

- Команда IRET, завершающая обработчик прерываний, восстанавливает прежнее состояние микропроцессора и передает управление прерванной программе.

Каскадное включение контроллеров приоритетных прерываний

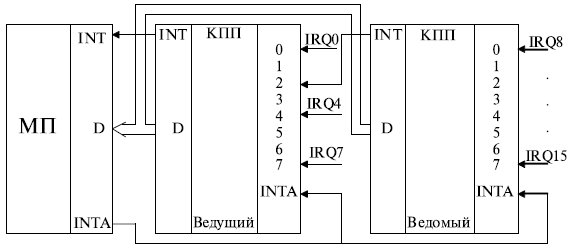

Для расширения количества запросов прерываний, которые могут быть подключены к микропроцессору, в микропроцессорной системе может быть использовано несколько КПП. Схема каскадного подключения двух контроллеров представлена на рис. 7.6.

К входу INT микропроцессора подключается выход INT ведущего контроллера. Выход INT ведомого контроллера подключается к одному из входов IRQi ведущего КПП на правах других запросов прерываний, поступающих на этот контроллер. В персональной ЭВМ всегда используются два контроллера приоритетных прерываний, причем ведомый КПП подключен к входу IRQ2 ведущего.

На рис. 7.5 было дано схематическое представление контроллера приоритетных прерываний. Для того чтобы лучше понять функционирование контроллеров приоритетных прерываний в реальных микропроцессорных системах и оценить все имеющиеся у них возможности, рассмотрим структуру КПП более подробно.

Регистры КПП делятся на 2 группы: регистры инициализации ICW1-ICW4 и операционные регистры OCW1-OCW3.

Регистры инициализации загружаются при инициализации контроллера и в процессе работы КПП не меняются.

Регистр ICW1 - управление микросхемой:

- настраивает контроллер на восприятие сигналов запроса по низкому уровню или заднему фронту;

- определяет, используется в МПС единственный КПП или применяется их каскадное включение;

- определяет порядок загрузки приказов инициализации. Необходимость этого обусловлена тем, что в пространстве ввода/вывода каждому контроллеру выделено всего 2 адреса. Так, в стандартной конфигурации персональной ЭВМ ведущему контроллеру выделены адреса 20h и 21h, а ведомому - A0h и A1h. В то же время каждый контроллер имеет в своем составе 7 регистров, к которым должен быть обеспечен программный доступ. В частности, при инициализации необходимо занести информацию в 4 регистра ICWi.

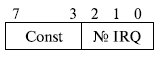

Регистр ICW2 - регистр типа прерывания. При инициализации в 5 его старших разрядов заносится некоторая константа. В процессе обработки запросов прерываний в 3 младшие разряда этого регистра заносится номер входа IRQi, по которому принят запрос, подлежащий обработке (рис. 7.7):

В персональной ЭВМ в регистр ICW2 ведущего контроллера при инициализации заносится константа 00001b, а в ведомый - константа 01110b. Поэтому типы всех прерываний, запросы от которых поступают через ведущий КПП, лежат в диапазоне 00001000b-00001111b (08h-0Fh), ачерез ведомый - в диапазоне 01110000b-01110111b (70h-77h). Распределение входов прерываний в стандартной конфигурации персональной ЭВМ представлено в табл. 7.1.

Регистр ICW3 - регистр управления ведомым. Имеет различное назначение в ведущем и ведомом КПП. В ведущем КПП устанавливаются единицы в разрядах, соответствующих линиям с подключенными ведомыми КПП. В персональной ЭВМ его значение имеет вид 00000100b. В ведомом КПП пять старших разрядов этого регистра установлены в 0, а в трех младших кодируется номер входа ведущего КПП, к которому подключен данный ведомый. В персональной ЭВМ его значение имеет вид 00000010b.

Регистр ICW4 - регистр управления режимом. Определяет, является данный КПП ведущим или ведомым, тип окончания прерывания, то есть кем должен сбрасываться бит запроса в регистре обслуживания прерывания ISR, и другие параметры работы.

Так как для КПП определено только 2 допустимых состояния (ведущий или ведомый), максимальная конфигурация контроллеров приоритетных прерываний состоит из 1 ведущего и 8 ведомых КПП. Это обеспечивает возможность подключения к входу INT микропроцессора до 64 запросов прерываний.

Содержимое операционных регистров изменяется в процессе работы КПП записью в них новой информации.

Регистр OCW1 ( IMR ) - регистр маски прерывания. Код 1 в разряде i запрещает, а код 0 - разрешает обработку запроса прерывания по входу IRQi.

Регистр OCW2 - определяет один из трех возможных порядков изменения приоритетов запросов прерываний:

- приоритеты не меняются в процессе работы КПП;

- приоритеты меняются циклически: после обработки очередного запроса его приоритет становится самым низким, а приоритеты остальных запросов циклически сдвигаются;

- процессе работы КПП какому-либо запросу можно задать наивысший приоритет, приоритеты остальных запросов при этом циклически сдвигаются.

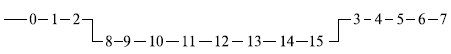

В персональной ЭВМ установлено постоянство приоритетов запросов прерываний, при этом запрос IRQ0 имеет самый высокий приоритет.

Так как здесь используются два каскадно включенных контроллера (см.рис. 7.6), приоритеты запросов прерываний IRQi имеют вид, представленный на рис. 7.8.

Регистр OCW3 - управляет переводом контроллера в режим неприоритетного обслуживания и считыванием содержимого регистра запросов IRR и регистра обслуживания ISR. В режиме неприоритетного обслуживания микропроцессор получает от КПП только сигнал запроса прерывания, после чего микропроцессор должен программно считать содержимое регистров IRR и ISR и по своим алгоритмам определить, какой из имеющихся запросов прерываний принять к обслуживанию.

Краткие итоги. В лекции рассмотрена классификация прерываний, порядок обработки прерываний в реальном и защищенном режимах работы микропроцессора, структура и функционирование контроллера приоритетных прерываний.