|

приветствую создателей курса и благодарю за доступ к информации! понимаю, что это уже никто не исправит, но, возможно, будут следующие версии и было бы неплохо дать расшифровку сокращений имен регистров итд, дабы закрепить понимание их роли в общем процессе. |

Лекция 2: Регистровая структура универсального микропроцессора

Регистровая структура универсального микропроцессора

В универсальном 32-разрядном микропроцессоре выделяют следующие группы регистров:

- основные функциональные регистры;

- регистры процессора с плавающей точкой;

- системные регистры;

- регистры отладки и тестирования.

Первые две группы регистров используются прикладными программами, последние две группы - системными программами, имеющими наивысший уровень привилегий.

Рассмотрим каждую из этих групп подробнее.

Основные функциональные регистры

В состав регистров этой группы входят:

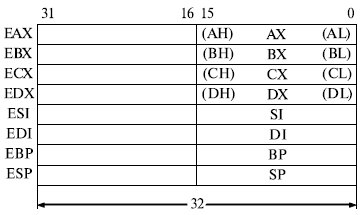

Состав и структура регистров общего назначения представлены на рис. 2.1.

Блок состоит из восьми 32-разрядных регистров. К каждому из них можно обращаться как к одному двойному слову (32 разряда).

Отметим, что понятие "слово" в данной архитектуре не идентично разрядности микропроцессора. Исторически сложилось так, что под словом понимается единица информации длиной 2 байта, или 16 двоичных разрядов. К младшим 16 разрядам регистров общего назначения можно обращаться так же, как и в 16-разрядном микропроцессоре (AX, BX…SP). Четыре 16-разрядных регистра AX, BX, CX, DX допускают обращение отдельно к своему старшему и младшему байту. Тем самым регистры позволяют на программном уровне работать либо с восемью 32-разрядными, либо с восемью 16-разрядными, либо с восемью 8-разрядными регистрами.

Все эти регистры используются для хранения промежуточных результатов вычислений и составных частей адреса при различных режимах адресации операндов, расположенных в памяти.

Кроме того, ряд регистров этого блока имеют свое, присущее только им назначение:

- EAX/AX/AL - регистр-аккумулятор, используется для сокращения длины команды при работе с непосредственными операндами;

- AX/AL - приемник (источник) данных в командах ввода (вывода) данных из (в) внешнего устройства;

- DX - определяет адрес ВУ в командах ввода (вывода) данных;

- ECX - используется в качестве счетчика циклов в командах циклов;

- BP, SP - используются при работе со стеком;

- ESI, EDI ( DI, SI ) - определяют положение строк в памяти в командах обработки строк.

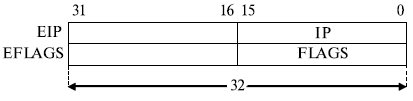

Регистр указателя команд и регистр флагов имеют длину 32 разряда.

Младшее слово каждого из этих регистров (разряды 0-15) функционально соответствует аналогичным разрядам в 16-разрядном микропроцессоре (рис. 2.2).

Регистр указателя команд EIP хранит смещение адреса команд относительно начала сегмента кода (сегмента команд).

Регистр флагов EFLAGS содержит признаки результата выполненной команды, а также разряды, управляющие работой микропроцессора: обработкой маскированных прерываний, последовательностью вызываемых задач, вводом-выводом и рядом других действий. Из этих флагов рассмотрим только наиболее значимые и интересные с точки зрения дальнейшего изучения работы микропроцессора.

К битам состояния регистра флагов относятся:

- ZF - признак нуля результата ( ZF = 1, если все разряды результата равны 0);

- SF - знак результата ( SF = 1, если старший разряд результата равен 1, то есть если результат отрицательный);

- OF - признак переполнения ( OF = 1, если при выполнении арифметических операций над числами со знаком происходит переполнение разрядной сетки);

- CF - флаг переноса ( CF = 1, если выполнение операции сложения приводит к переносу за пределы разрядной сетки), устанавливается также в некоторых других операциях;

- PF - признак четности (дополняет до нечетного числа единиц младший байт результата);

- AF - флаг полупереноса (используется при операциях над двоичнодесятичными числами);

- DF - устанавливается пользователем и определяет порядок обработки строк символов в соответствующих командах: декремент (при DF = 1 ) или инкремент (при DF = 0 ) содержимого индексных регистров ESI, EDI ( SI, DI ) после обработки одного символа.

В состав флагов управления входят:

- IF - флаг прерываний (при IF = 1 разрешается обработка маскированных аппаратных прерываний);

- TF - флаг ловушки, или трассировки (при ТF = 1 после выполнения каждой команды возникает прерывание, используемое отладчиками;);

- NТ - бит вложенной задачи (показывает, что данная задача была вызвана из другой программы, аналогично подпрограмме, и возврат из этой задачи должен проводиться по механизму переключения задач);

- IOPL - 2-разрядное поле уровня привилегий ввода/вывода (определяет уровень привилегий программ, которым разрешено выполнение операции ввода-вывода);

- VM - режим виртуального микропроцессора i8086 (при работе микропроцессора в защищенном режиме установка VM = 1 вызывает переключение в режим виртуального микропроцессора i8086; в этом случае микропроцессор функционирует как быстрый МП i8086, но реализует механизмы защиты памяти, страничной адресации и ряд других дополнительных возможностей; бит VM может быть установлен только в защищенном режиме).

Блок сегментных регистров состоит из шести 16-разрядных регистров, которые указывают на различные сегменты, расположенные в памяти компьютера:

- CS ( Code Segment ) - сегмент кода программы;

- DS ( Data Segment ) - сегмент данных;

- SS ( Stack Segment ) - сегмент стека;

- ES, FS, GS - дополнительные сегменты данных.

При работе микропроцессора в реальном режиме в сегментном регистре содержатся старшие 16 разрядов 20-разрядного базового адреса сегмента. Физический адрес начала сегмента получается умножением этой величины на 16:

Получающийся 20-разрядный адрес позволяет адресовать память емкостью 220 байт = 1 Мбайт. При этом сегменты имеют постоянную длину 216 байт. Разработчики первых персональных компьютеров полагали, что оперативная память, большая чем 1 Мбайт, никогда не потребуется пользователю, поэтому вся архитектура строилась исходя именно из этого положения.

При переходе к 32-разрядной архитектуре стало необходимым обеспечить возможность адресации памяти емкостью до 232 байт. Кроме того, введение защищенного режима работы микропроцессора потребовало хранения большого количества дополнительной информации о сегменте: его длине, которая стала переменной, уровне привилегий, его типе и т. д. Простое увеличение разрядности сегментных регистров до 32 бит не обеспечило бы возможности хранения всей этой информации. Поэтому все данные о сегменте стали размещаться в специальных структурах - дескрипторах (описателях) сегментов, которые хранятся в таблицах дескрипторов, расположенных в памяти, а сегментные регистры, сохранив свою первоначальную длину в 16 разрядов, содержат так называемый селектор (указатель), который используется для того, чтобы найти нужный дескриптор в этих таблицах.

Регистры процессора с плавающей точкой

К этой группе регистров относятся (рис. 2.3):