|

приветствую создателей курса и благодарю за доступ к информации! понимаю, что это уже никто не исправит, но, возможно, будут следующие версии и было бы неплохо дать расшифровку сокращений имен регистров итд, дабы закрепить понимание их роли в общем процессе. |

Мультипрограммный режим работы микропроцессора

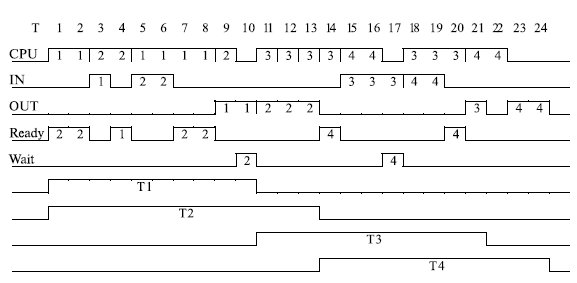

Полученная диаграмма выполнения программ представлена на рис. 6.2.

Построив аналогичную диаграмму работы ЭВМ для Км = 3, получим результаты, представленные в табл. 6.2 (Км = 1 соответствует однопрограммной работе ЭВМ, и результаты для этого случая могут быть получены расчетными методами).

Анализ показывает, что с увеличением коэффициента мультипрограммирования пропускная способность ЭВМ будет увеличиваться, стремясь к некоторому пределу, определяемому характеристиками ресурсов ЭВМ. В то же время каждая программа будет выполняться в общем случае более длительное время из-за необходимости ожидания освобождения ресурсов, занятых другими программами. При увеличении коэффициента мультипрограммирования изменение значений показателей эффективности зависит от того, в каком состоянии находится система: перегрузки или недогрузки. Если какие-либо ресурсы ЭВМ задействованы достаточно интенсивно, то добавление новой программы, активно использующей эти ресурсы, будет малоэффективным.

Микропроцессор для поддержки мультипрограммного режима работы использует определенный набор аппаратных средств.

В компьютере, работающем в мультипрограммном режиме, выделяется область памяти, доступная только операционной системе, в которой хранится вся информация, необходимая для рестарта задачи (контекстная память, или кадр состояния). При переключении контекста компьютер просто переходит от одного раздела к другому. В качестве такого раздела в универсальных микропроцессорах выступает сегмент состояния задачи TSS, который является небольшим сегментом данных с разрешенными операциями считывания и записи, - доступ к нему не разрешается никаким программам, даже на самом высоком уровне привилегий. К сегментам TSS может обращаться только сам процессор.

Для поддержки работы с сегментом состояния задачи служит 16-разрядный регистр задачи TR, в который заносится селектор дескриптора TSS, и связанный с TR программно недоступный 64-разрядный "теневой" регистр, в который загружается дескриптор TSS. Дескрипторы сегментов состояния задач хранятся только в глобальной таблице дескрипторов GDT. Для переключения задач используется шлюз задачи.

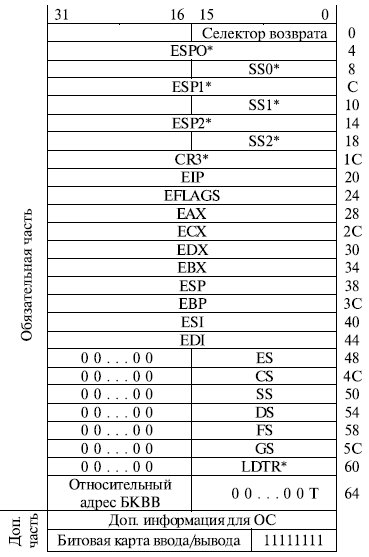

Сегмент состояния задачи состоит из двух частей (рис. 6.3). Обязательная часть TSS объемом 104 байта содержит информацию, необходимую для рестарта данной задачи после ее вызова на исполнение, а также некоторую другую информацию. Дополнительная часть может содержать какую-либо информацию о задаче, используемую операционной системой (имя задачи, комментарии и т. д.), и битовую карту ввода/вывода (БКВВ), определяющую устройства ввода/вывода, к которым разрешено обращение данной задачи при определенных ситуациях.

Содержимое ряда полей TSS не изменяется при решении задачи (на рис. 6.3 они помечены звездочкой): селектор LDT данной задачи (то есть регистр LDTR ), регистр управления CR3 (базовый адрес каталога таблиц страниц ), поля SSi и ESPi, которые определяют начальные адреса стеков при переключении к задачам с более высоким уровнем привилегий, что обеспечивает их более надежную защиту.

При переключении задачи процессор может перейти к другой локальной таблице дескрипторов LDT и перезагрузить базовый регистр каталога страниц CR3. Это позволяет назначить каждой задаче свое отображение логических адресов на физические, что служит дополнительным средством защиты, так как задачи можно изолировать и предотвратить их взаимодействие друг с другом.

Поле селектора возврата обеспечивает связь данной задачи с вызвавшей ее программой. Селектор возврата - это селектор TSS предыдущей задачи, при выполнении которой произошел вызов данной задачи ( TR предыдущей задачи, если предполагается возврат к ней).

Бит ловушки T используется при отладке программного обеспечения аналогично биту TF в регистре флагов: если T = 1, то при переключении на данную задачу возникает прерывание.

В TSS отсутствуют поля для хранения регистров управления CR0 и CR2. Это означает, что их содержимое не меняется при переключении задач. Следовательно, страничное преобразование и условия работы с FPU являются глобальными для всех задач. Для каждой задачи может быть свой каталог таблиц страниц, но страничное преобразование может быть разрешено или запрещено только для микропроцессорной системы в целом.

Объем дополнительной части TSS зависит от количества служебной информации ОС, определяемой характером решаемой задачи, и размеров применяемой битовой карты ввода/вывода. Дополнительная часть TSS может вообще отсутствовать.

Относительный адрес БКВВ определяет положение битовой карты в TSS. Каждый бит БКВВ соответствует однобайтовому порту ввода/вывода. Так как микропроцессор может обращаться к 216 портов, полная битовая карта ввода/вывода, определяющая возможность их обслуживания, -

это строка длиной до 64 Кбит. Когда для задачи определена БКВВ, ей предоставляется дополнительная возможность выполнения команд ввода/вывода. Если обычная защита по привилегиям запрещает ввод/вывод (уровень привилегий задачи меньше уровня, установленного в поле IOPL регистра флагов), процессор обращается к БКВВ для дополнительной проверки возможности ввода/вывода на конкретных устройствах. Если соответствующие этим адресам биты карты содержат нули, то операции ввода/вывода разрешаются. В противном случае формируется особый случай нарушения защиты. Таким образом, БКВВ обеспечивает задаче свободный доступ к незащищенным портам ввода/вывода без требования понижения значения в поле IOPL регистра флагов.

За последним байтом БКВВ в TSS должен следовать заключительный байт, состоящий из одних единиц. Адрес этого байта должен соответствовать границе сегмента, определенной дескриптором TSS.

После поле предела должна быть указана длина не менее 104 байт (длина обязательной части TSS ). Если указанный размер сегмента меньше 104 байт, то происходит прерывание.

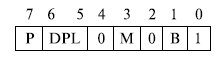

Байт доступа дескриптора TSS имеет следующий вид (рис. 6.4):

У него есть ряд особенностей по сравнению с дескрипторами обычных сегментов.

Бит занятости B устанавливается в 1 при переключении на данную задачу. Используется для обнаружения попытки вызова задачи, выполнение которой прервано. Переключение задач производится, только если B = 0.

При B = 1 возникает прерывание. Установка B = 1 в дескрипторе TSS производится командами JMP и CALL, переключающими микропроцессор на выполнение данной задачи. При этом другие обращения в мультипрограммной системе к этой задаче будут запрещены.

В байте доступа дескриптора TSS поле DPL не означает уровень привилегий самого сегмента состояния задач, а аналогично функции поля DPL шлюза вызова показывает, какие программы могут обращаться к задаче, которая определяется данным дескриптором TSS.

Значение M = 0 обеспечивает совместимость с микропроцессором i286, в котором впервые появился мультипрограммный режим работы.