|

Здравствуйте! Прошел курс, а где экзамен? Как сертификат получить? Без экзамена? |

Последовательностная логика. Регистры

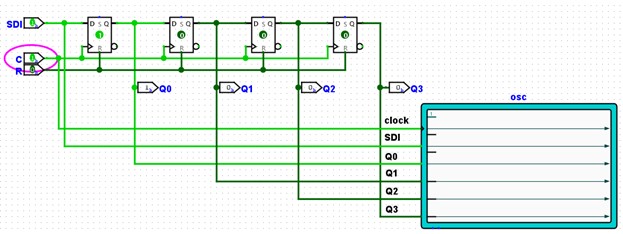

- SDI - serial data input, последовательный вход данных. Данный вход подключается к младшему триггеру регистра;

- С - объединяющий все триггеры, вход управления синхронизации (в данном примере по переднему фронту);

- R - reset, объединяющий все триггеры асинхронный вход сброса;

- Q0-Q3 - quit, параллельный выход данных.

Триггеры объединяются следующим образом: прямой выход младшего триггера подключается к входу D старшего триггера. В сдвиговых регистрах старший триггер может иметь дублирующий Q выход SDO - serial data output, последовательный выход данных.

Для закрепления информации предлагается реализовать описываемый регистр. К нему подключить инструмент цифровой осциллятор (осциллограф) для наблюдения операции сдвига. В качестве тестового сигнала будет подан сигнал "1" на вход SDI. Перед вторым тактом он будет снят. В итоге на последнем такте синхросигнала двоичный код на выходе регистра должен иметь вид 1000. На рисунках 4.18 - 4.20 показано начало, промежуточное значение и окончание процесса моделирования. Провода, идущие к осциллографу, для информативности подписаны инструментом "Редактировать текст". Свойство осциллографа "Количество входов" задано равным 5.

Обычно при создании параллельно-последовательных сдвиговых регистров, параллельные входы данных подключаются к асинхронным входам установки (S) и сброса (R) триггеров. Для параллельной записи в регистр добавляется дополнительный вход управления, обозначаемый обычно PE - parallel enable, разрешение записи. Управление входами данных обычно реализуется на двухвходовых логических элементах "И" (AND) или И-НЕ (NAND).

Запись в регистр параллельного кода в данном примере не зависит от проводимых операций сдвига. На рисунке 4.21 приведена функциональная схема параллельно-последовательного регистра.

Существуют реверсивные сдвигающие регистры, сдвигающие в сторону старших или младших разрядов в зависимости от управляющих сигналов. На рисунке 4.22 приведена функциональная схема такого регистра, где входы имеют следующие обозначения:

- DSI - последовательный вход данных;

- R - асинхронный сброс регистра,

- C - вход синхронизации (Clock), обеспечивающий сдвиг данных;

- DSR - data shift right, прямой вход управления сдвигом вправо;

- DSL - data shift left, прямой вход управления сдвига влево.

Принцип работы регистра следующий. Зафиксировать сигнал управления DSR лог. "1". Подать сигнал на вход DSI и синхросигналы на вход С. Логическая 1 в триггерах будет смещаться в сторону старших разрядов. Если снять сигнал с входа DSR и DSI и подать сигнал на вход DSL, то можно пронаблюдать обратный процесс.

У последнего триггера в схеме управления сдвигом влево один из входов элемента "И" подключен к лог. "0", что обеспечит очистку регистра при сдвиге данных влево.

В листинге 4.2 приведен код на языке Verilog HDL четырехразрядного сдвигового регистра, функционирующего аналогично, приведённого на рисунке 4.22.

module shift_register (

input wire C, // Синхровход

input wire R, // Асинхронный сброс (активный высоки уровень)

input wire DSI, // Входные данные для сдвига

input wire DSL, // Управляющий сигнал сдвига влево

input wire DSR, // Управляющий сигнал сдвига вправо

output reg [3:0] Q // 4-разрядный выход

);

always @(posedge C or posedge R) begin

if (R)

begin

Q <= 4'b0000; // Сброс регистра

end

else begin

if (DSL && !DSR)

begin

// Сдвиг влево

Q <= {Q[2:0], DSI}; // Сдвинуть влево и добавить d_in

end

else if (DSR && !DSL)

begin

// Сдвиг вправо

Q <= {DSI, Q[3:1]}; // Сдвинуть вправо и добавить бит по //линии DSI

end

// Если оба сигнала неактивны, значение регистра остается без изменений

end

end

endmodule

Листинг

4.2.