|

Здравствуйте! Когда появится возможность сдать экзамен на сертификат? |

Кэш-память

КЭШ-ПАМЯТЬ МНОГОЯДЕРНЫХ ПРОЦЕССОРОВ

Реализация кэш-памяти многоядерных процессоров, да и в целом вычислительных устройств с аппаратной поддержкой многозадачности, сопряжена с рядом трудностей. Одна из наиболее значительных трудностей вызвана необходимостью обеспечить когерентность кэш-памяти.

Когерентность - свойство многоядерного процессора, подразумевающее согласованность данных в кэш-памяти его разных ядер при исполнении программ.

Рассмотрим пример сбоя, который может произойти при использовании кэш-памяти, не обладающей свойством когерентности. Допустим, что в программе на С есть такая строка int x, y. В оперативной памяти эти переменные размещаются рядом и попадают в один блок, который передается в кэш-память и потом, через некоторое время, "возвращается" в оперативную память из кэш-памяти. Далее предположим, что у нас имеется двухъядерный процессор, и каждое из ядер меняет одну из этих переменных - ядро 1 меняет переменную x, а ядро 2 меняет переменную y (это может происходить, например, в разных потоках нашей программы). Таким образом, процессор выполняет следующие действия.

- Ядро 1 читает значение переменной x, записывая в свою кэш-память соответствующий блок оперативной памяти.

- Ядро 2 читает значение переменной y, записывая в свою кэш-память тот же блок оперативной памяти (напоминаем, что обе переменные находятся рядом, а кэш-память и оперативная память не могут обмениваться фрагментами памяти, соответствующими только одной переменной, и захватывают лишнее; в этом-то и проблема!).

- Ядро 1 записывает новое значение в переменную x в своей кэш-памяти.

- Ядро 2 записывает новое значение в переменную y в своей кэш-памяти.

- В оперативную память записывается строка кэш-памяти ядра 1; данная строка содержит как измененное значение переменной x, так и прежнее значение переменной y.

- В оперативную память записывается строка кэш-памяти ядра 2 данная строка содержит старое значение переменной x, так и измененное значение переменной y.

Очевидно, что на шаге 6 значение переменной x окажется прежним, которое было до того, как ядро 1 изменило эту переменную. Таким образом результаты действий ядра 1 по изменению переменной x окажутся потерянными, что является ошибкой.

Для того, чтобы избежать таких проблем, сохранив при этом эффективность работы кэш-памяти, в многоядерных процессорах приходится применять сложные технические решения.

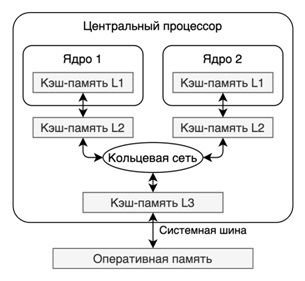

В качестве примера рассмотрим процессор Intel Core i7 (рис.11.2). Этот процессор имеет трёхуровневую кэш-память. Внутри каждого ядра находится кэш-память первого уровня (L1); она является самой быстрой. Для повышения производительности кэш-память уровня L1 организована по принципу гарвардской архитектуры: машинный код и данные хранятся в ней раздельно. Кэш-память второго уровня (L2) имеет больший объём и меньшее быстродействие, в ней код и данные хранятся вместе. У каждого процессорного ядра имеется своя кэш-память второго уровня, и другие ядра с ней работать не могут. Наконец, кэш-память третьего уровня (L3) является общей для всех ядер, и она оказывается самой большая, но и самой медленной. Посредством кэш-памяти уровня L3 процессор обращается к системной шине для доступа к оперативной памяти.

Для обеспечения когерентности внутри процессора Intel Core i7 используется внутренняя шина специальной конструкции, которая называется кольцевой сетью. К ней последовательно подключены несколько кэши разных ядер. Получив запрос на предоставление данных, каждый из них решает, обработать ли этот запрос, или передать его дальше. Когда ядро 1 на рис. 11.2 обращается к блоку памяти, копии которого нет в его внутренней кэш-памяти L1, этот запрос обрабатывает его кэш L2. Если требуемые данные нашлись в кэш-памяти L2 ядра 1, то она возвращает их ядру 1. Если же в кэш-памяти L2 ядра 1 не нашлось нужных данных, то запрос кэш-памяти L2 следующего ядра - в данном случае ядра 2. Если в кэш-памяти L2 ядра 1 требуемые данные нашлись, то этот она обрабатывает запрос и возвращает дынные в кэш-память L2 ядра 0. Если ни в одном кэшей L2 ни нашлось требуемых данных, запрос возвращается необработанным ядру 1, и концевая сеть повторно направляет его уже в кэш-память L3 (который в случае промаха обращается уже к оперативной памяти). Как только какое-то из ядер вносит изменения в кэш-данные, кольцевая сеть отправляет остальным ядрам сообщение о том, что копии этих данных в их кэш-памяти потеряли актуальность, и в случае последующих обращений их надо будет запросить у изменившего их ядра. В рассмотренном выше примере с кэшированием двух переменных x и y из разных потоков концевая сеть внесет следующие изменения в действия процессора (в этом примере мы описываем то, как это происходит в процессоре Intel Core i7).

- На шаге 3) ядро 1 по кольцевой сети сообщает, что все копии блока памяти, за исключением той, которая находится в кэш-памяти ядра 1, становятся неактуальными.

- На шаге 4), прежде чем менять значение переменной y, ядро 2 запрашивает актуальные данные строки кэш-памяти у ядра 1. Затем меняет значение переменной y. А после изменения сообщает ядру 1, что актуальная копия теперь у него.

- Шагов 5) и 6) не будет, поскольку ядра процессора Intel Core i7 не взаимодействуют c оперативной памятью самостоятельно. Вместо этого в какой-то момент актуальная копия блока памяти попадёт из кэш-памяти ядра 2 в общую кэш-память L3, а ещё позже из L3 - в оперативную память.

Вопросы

- Дайте определение кэш-памяти процессора.

- Назовите основные характеристики кэш-памяти.

- Что такое механизм отображения кэш-памяти?

- Зачем нужна иерархическая кэш-память?

- Что такое механизм прямого отображения кэш-памяти?

- Что такое механизм ассоциативного отображения кэш-памяти?

- Что такое механизм смешанного отображения кэш-памяти?

- Опишите процедуру выполнения операции замещении

- Расскажите про LRU-стратегию.

- Что такое принцип Белэди?

- Расскажите, в каких отношениях находится прикладная программа с кэш-памятью?

- Что такое принцип локальности?

- Приведите пример соблюдения локальности при программировании на языке С.

- Приведите пример несоблюдения принципа локальности при программировании на языке С.

- Проверьте на практике, что программа, описанная в лекции и не соблюдающая принцип локальности, будет работать медленнее, чем та, в которой этот принцип соблюдается.

- Что такое когерентность кэш-памяти?

- Расскажите, как с помощью кольцевой сети реализуется когерентность кэш-памяти ядер в процессоре Intel Core i7?

Литература

- Орлов С.А., Цилькер Б.Я. Организация ЭВМ и систем: Учебник для вузов. 2-е изд. СПб.: Питер, 2011. 688 с.

- Таненбаум Э., Остин Т. Архитектура компьютера. 6-е изд. СПб.: Питер, 2013. 816 с.

- Bahn H., Noh, S. H. Characterization of Web reference behavior revisited: Evidence for Dichotomized Cache management // International Conference on Information Networking 2003. Jeju, South Korea: Springer-Verlag. P. 1018-1027.