Страничная организация памяти

Реализация таблицы страниц

Использование ассоциативной памяти.Таблица страниц – непрерывная область физической памяти. В системе имеется базовый регистр таблицы страниц (page table base register – PTBR),указывающий на таблицу страниц и хранящий ее длину.

Таким образом, при страничной организации любой доступ к памяти требует фактически не одного, а двух обращений в память – одно в таблицу страниц, другое – непосредственно к данным или команде. В этом – некоторый недостаток и неэффективность страничной организации, по сравнению с более простыми методами управления памятью.

В системах с теговой архитектурой, например, "Эльбрус", регистр таблицы страниц ( регистр таблицы страниц пользователя – РТСП) содержит дескриптор таблицы страниц, который, кроме ее адреса, содержит также ее длину.

Проблема двух обращений решается введением ассоциативной памяти (cache) страниц,называемой также буфер трансляции адресов (translation lookaside buffer – TLB).Ассоциативная память, по существу, является ассоциативным списком пар вида: (номер страницы, номер фрейма).Ее быстродействие значительно выше, чем у основной памяти и у регистров.

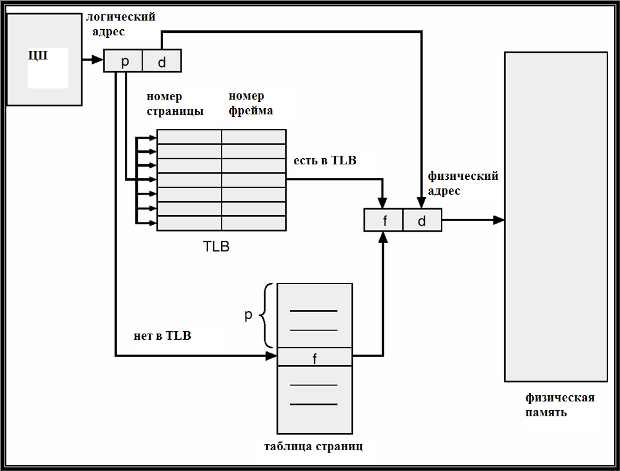

Схема трансляции адресов с использованием ассоциативной памяти изменяется: если номер страницы из логического адреса найден в ассоциативной памяти, то из ее элемента извлекается соответствующий номер фрейма.Если же номер страницы отсутствует в ассоциативной памяти, он выбирается обычным образом из таблицы страниц, но заносится в ассоциативную память. Таким образом, в ассоциативной памяти накапливается информация о наиболее часто используемых страницах.

Модифицированная схема трансляции адресов с использованием TLB иллюстрируется рис. 16.7.

Оценка среднего времени доступа к памяти с использованием TLB

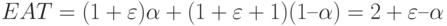

Предположим, что ассоциативный поиск в среднем требует  единиц времени. Цикл памяти примем за 1. Введем также еще один показатель – число

единиц времени. Цикл памяти примем за 1. Введем также еще один показатель – число  от 0 до 1 ( hit ratio ), характеризующее, сколько раз (в среднем) номер страницы будет найден в TLB, - эмпирическую вероятность нахождения номера страницы в ассоциативной памяти.

от 0 до 1 ( hit ratio ), характеризующее, сколько раз (в среднем) номер страницы будет найден в TLB, - эмпирическую вероятность нахождения номера страницы в ассоциативной памяти.

Вычислим математическое ожидание времени доступа – Effective Access Time (EAT).Вероятность того, что номер страницы не будет найден в TLB, равна 1 –  . Тогда получим:

. Тогда получим:

Защита памяти

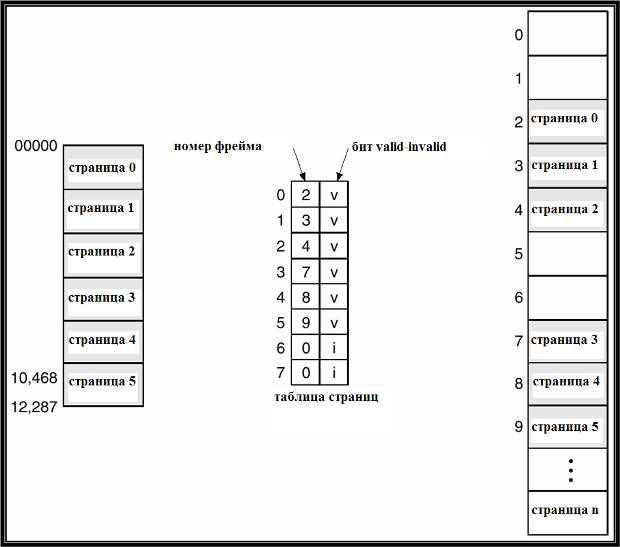

При адресации с помощью страничной организации возможно, что логический адрес сформирован неверно, и его номер страницы выходит за пределы логической памяти процесса. Защита от неверной адресации может быть реализована хранением и проверкой дополнительного бита valid-invalid в каждом элементе таблицы страниц. Значение valid указывает, что страница с данным номером принадлежит логической памяти процесса, значение invalid – что это не так.

Организация защиты памяти процесса с помощью бита valid-invalid иллюстрируется на рис. 16.8.

В примере процесс имеет 6 логических страниц с номерами от 0 до 5. Таблица страниц имеет длину 8 (с элементами от 0 до 7). Элементы 6 и 7 не соответствуют логическим страницам процесса, поэтому в них биты valid-invalid установлены в значение invalid. Поэтому при попытке обращения по логическому адресу с номером страницы 6 или 7 произойдет прерывание по неверной адресации.

Структура таблицы страниц

Иерархические таблицы страниц.Таблицы страниц в операционных системах могут быть по-разному организованы, при сохранении общих принципов их использования, описанных ранее. Рассмотрим далее три основных способа организации таблиц страниц – иерархические таблицы страниц, хешированные таблицы страниц и инвертированные таблицы страниц.

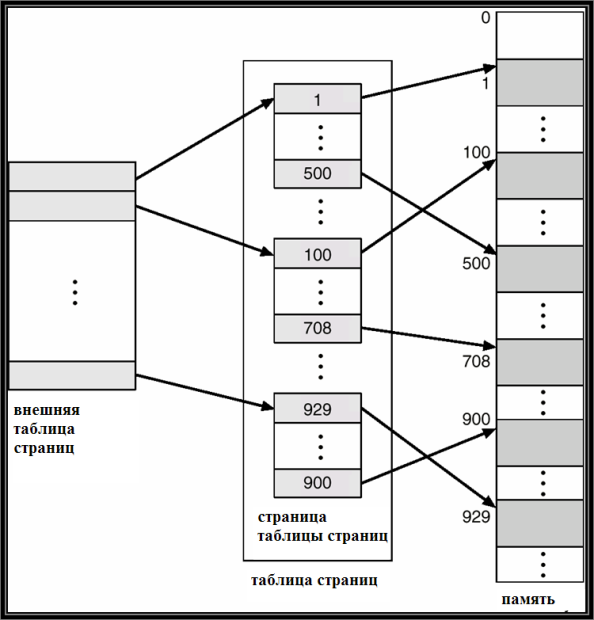

Чаще всего используются иерархические таблицы страниц.При их использовании логическое адресное пространство разбивается на несколько таблиц страниц (иначе говоря, используются таблицы таблиц страниц ). Наиболее простой и распространенный метод – двухуровневая таблица страниц.

При обычной организации таблицы страниц, логический адрес (для 32-разрядной архитектуры, при размере страницы 4 килобайта = 4096 байтов) разбивается на номер страницы (20 битов) и смещение внутри страницы (12 битов).

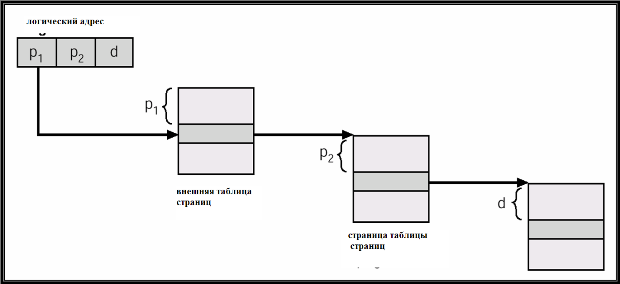

При двухуровневой организации таблицы страниц, таблица страниц верхнего уровня сама делится на страницы, поэтому логический адрес будет иметь вид: (p1, p2, d),где p1 – индекс во внешней таблице страниц, p2 – смещение внутри страницы для внешней таблицы страниц, d – смещение внутри страницы (адресуемой по внутренней таблице страниц). При тех же предположениях об архитектуре и размере страницы, p1 и p2 будут занимать по 10 битов.

Организация двухуровневых таблиц страниц изображена на рис. 16.9.

Схема адресной трансляции по двухуровневой таблице страниц иллюстрируется рис. 16.10.