|

Добрый день, Я прошёл платный курс по программе «Архитектурные решения на базе аппаратных платформ IBM» получил диплом №ПК 100848460. Как мне получить его ? Вы отправите его почтой ? |

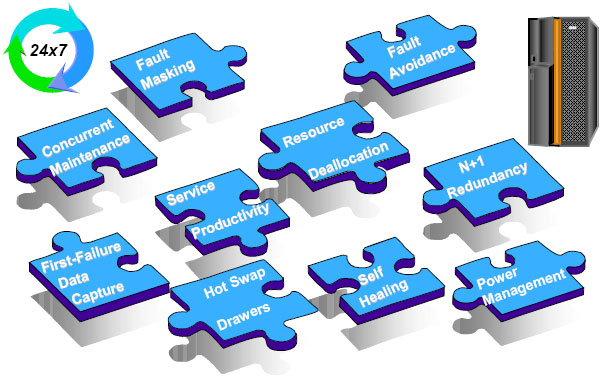

Reliability, Availability, Serviceability (RAS)

Компоненты RAS

Вот лишь некоторые функции, применяемые в серверах pSeries, позволяющие существенно повысить надежность аппаратно- программных комплексов:

- Автоматический сбор данных об отказах и диагностика возможностей локализации неисправностей.

- Самовосстанавливающиеся после сбоев внутренние процессорные матрицы

- Первая промышленная шина PCI с восстановлением после ошибок четности

- Динамическое исправление ошибок

- Применение кодов коррекции ошибок (ECC) для оперативной памяти и кэш 1,2 и 3 уровней.

- Технология Chipkill для коррекции ошибок оперативной памяти

- Предсказание возникновения ошибок процессора, кэш, оперативной памяти, подсистемы ввода/вывода

- Отключение процессора во время работы и в процессе загрузки системы (Dynamic Processor Deallocation, Persistent Processor Deallocation)

- Диагностика в реальном времени, основанная на сборе данных об отказах подсистемы питания, охлаждения и ввода/вывода

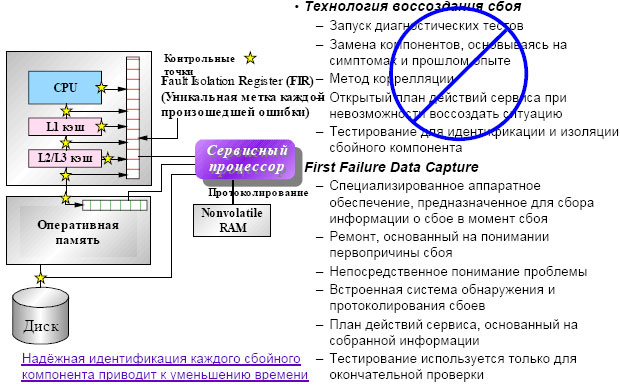

Сбор информации об ошибках в реальном времени

- First Failure Data Capture предоставляет информацию об ошибках в реальном времени и дает возможность определить компоненты (FRU/s), необходимые для устранения проблемы

- Попытки воссоздать ситуацию, приведшую к сбою, могут занять много времени, быть неэффективными или невозможными

Основываясь на данных об использовании серверов без возможности диагностики отказов в реальном времени, можно сказать, что серьезные отказы случаются в 2-3 раза чаще, если диагностика в реальном времени не используется. Система не может деконфигурировать какой-либо неисправный элемент, если его нельзя продиагностировать. Опыт и сравнение данных об эксплуатации серверов с и без возможности диагностики показывают, что сервера с такой возможностью имеют значительные преимущества.

Диагностика в системах pSeries выявляет примерно 95% отказов в FRU (Field Replaceable Unit). В остальных 5% случаях можно вручную выявить отказ. Для достижения таких показателей используется система датчиков, расположение которых хорошо продумано.

Сервисный процессор

- Отдельный микропроцессор

- Независим от основных процессоров

- Повышение доступности и управляемости системы

- Изолированное электропитание, энергонезависимая память (EPROM), доступ по последовательному порту

- В POWER5: доступ по TCP/IP

- Доступ с HMC (Ethernet)

- Встроенный Web-интерфейс

- Автоматические действия

- Удаленное управление – включение системы, диагностика, настройка

Сервисный процессор – это отдельный независимый процессор, который обеспечивает инициализацию устройств во время IPL, оперативное наблюдение за случаями возникновения ошибок, а так же помогает в техническом обслуживании серверов pSeries. Абсолютно все датчики снабжены доступными для чтения регистрами (Fault Isolation Register) и блокирующей логикой, которая обеспечивает запись обнаруженной ошибки только одним датчиком. Такой вид диагностики улучшает качество других форм диагностирования, таких, как BIST, который чаще выявляет постоянные отказы, а не случайные, возникающие только во время работы. Диагностика в реальном времени является детерминистической, так как для каждого датчика определено и задокументировано свое уникальное множество ошибок. Корректность диагностики проверяется следующим образом: в случайные моменты времени создаются условия для возникновения отказа и проверяется правильный ли компонент выявила диагностика. Например, в системе p690 установлено более 15000 внутренних датчиков, а общий размер FIR составляет свыше 5600 бит.

Технология FFDC

Для проведения диагностики в реальном времени, сервисный процессор "общается" с сервером через сигналы предупреждения (Attention signals) и специальный порт JTAG, посредством операций записи/чтения из/в него. Операции записи/чтения из регистров FIR асинхронны и прозрачны для работы системы. Другими словами, о существовании регистров FIR "знает" только сервисный процессор.

При выявлении ошибки в каком-либо устройстве система посылает сервисному процессору соответствующий сигнал предупреждения. В ответ на такой сигнал сервисный процессор читает содержимое соответствующего регистра FIR и, анализируя структуру "Who’s On First", проверяет активные биты и записывает идентификатор этого регистра в NVRAM. NVRAM служит как бы буфером между сервисным процессором, системным ПО и ОС AIX. Идентификатор регистра вместе с сообщением о природе ошибки системным ПО записывается в лог ошибок AIX. После восстановления сервисный процессор сбрасывает регистры. Теперь они снова могут протоколировать случаи возникновения ошибок.

Тщательный дизайн

- Компоненты и технологии уровня мэйнфрэймов

- Пониженное энергопотребление, сниженная рабочая температура позволяют повысить надежность

- Специальный дизайн процессорных блоков и карт памяти

- Самонаправляющие рельсы для установки карт памяти, PCI адаптеров и процессорных модулей помогают избежать повреждения контактов

Основная конструкторская работа при разработке линейки pSeries была направлена на анализ и выявление критических точек в CEC для того, чтобы или совсем их исключить или добиться снижения вероятности отказа. Лучший способ сделать систему отказоустойчивой - это, в первуюочередь, предотвратить появление ошибок. Компоненты внутри CEC спроектированы таким образом, чтобы обеспечить уровень надежности, сравнимый с мэйнфреймами. Они проходят дополнительное тестирование в экстремальных условиях и подвергаются более жесткому отбору, чем стандартные промышленные компоненты, устанавливаемые в обычных UNIX-серверах.