|

Добрый день, Я прошёл платный курс по программе «Архитектурные решения на базе аппаратных платформ IBM» получил диплом №ПК 100848460. Как мне получить его ? Вы отправите его почтой ? |

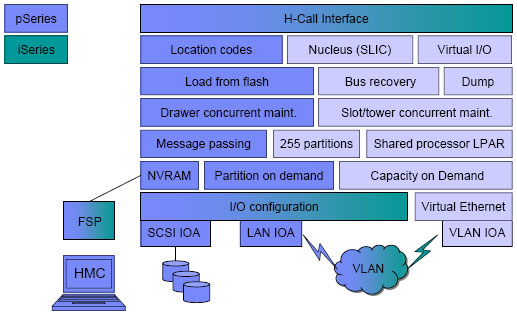

Технологии виртуализации (POWER)

POWER Hypervisor

Компоненты POWER Hypervisor

Это - упрощенная диаграмма, показывающая источник различных элементов в гипервизоре POWER.

Синие поля показывают функции, которые пришли непосредственно от существующего гипервизора pSeries POWER4 или от архитектуры pSeries. Фиолетовые поля (более светлые) показывают поля, пришедшие от от iSeries SLIC (System Licensed Internal Code) - который является частью OS/400.

Некоторые поля - смешанные, и они представляют функции, которые объединяют элементы pSeries и iSeries.

Функции гипервизора

- Динамические разделы (DLPAR)

- Capacity Upgrade on Demand

- Микроразделы

- Общий пул процессоров

- Virtual I/O

- Virtual LAN

Гипервизор POWER предоставляет те же самые основные функции как гипервизор POWER4, плюс некоторые новые функции, разработанные для разделов, работающих в общем процессорном пуле и виртуального ввода - вывода.

Объединенный с особенностями, имеющимися в процессоре POWER5, гипервизор POWER предоставляет дополнительные функции, включая микроразделы, виртуальные процессоры, IEEE VLAN совместимый виртуальный коммутатор, виртуальные SCSI адаптеры и виртуальные консоли.

Гипервизор POWER - компонент встроенного программного обеспечения (firmware) системы, которое всегда устанавливается, независимо от системной конфигурации. Он работает как скрытый раздел, без выделенной процессорной емкости.

Специально разработанные запросы к гипервизору (hcalls) обеспечивают для операционной системы способ связи с гипервизором, позволяя более эффективно использовать физическую емкость процессора.

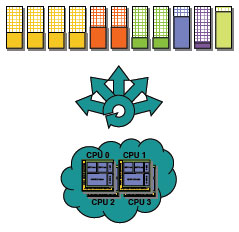

Диспетчеризация процессоров

Управление набором процессоров в системе (shared processor pool).

Квант времени в POWER5 - 10 мс

- Квант времени в POWER5 - 10 мс

- Минимальное выделение - 1 мс на физический процессор

- Каждый виртуальный процессор гарантированно получает свое количество процессорных тактов (capacity entitlement) в пределах окна (10 мс)

- ms/VP = CE * 10 / VPs

Общая емкость разделов равномерно распределяется между виртуальными процессорами

Логические разделы, работающие в общем процессорном пуле, требуют надежного механизма гарантирования правильного распределения свободных процессорных тактов.

Каждый микрораздел конфигурируется с конкретной процессорной емкостью, базирующейся на количестве processing units - entitled capacity или capacity entitlement (CE).

Выделенная емкость, вместе с определенным количеством виртуальных процессоров, определяет физические процессорные ресурсы, которые будут выданы разделу.

Объем времени, в течение которого работает виртуальный процессор до окончания кванта, основывается на правах раздела, определяемых системным администратором. Права разделов равномерно распределяются между работающими виртуальными процессорами, поэтому число виртуальных процессоров влияет на продолжительность рабочего цикла каждого процессора.

Гипервизор использует архитектурный принцип "колеса распределения" с фиксированным периодом вращения, равным X миллисекунд, в течение которого каждый процессор своевременно получает свою долю ресурсов. Время виртуальных процессоров распределяется с помощью аппаратного вычитателя, подобно тому, как операционная система разделяет время между процессами.

Диспетчеризация и задержки

- Виртуальные процессоры имеют задержку диспетчеризации

- Задержка (dispatch latency) – это время, в течение которого виртуальный процессор становится работоспособным и реально диспетчеризируется

- Счетчики и внешние прерывания также имеют задержку

Виртуальные процессоры имеют задержку диспетчеризации. Когда виртуальные процессор становится готовым к работе, он помещается в очередь гипервизора, где он и находится до момента диспетчеризации. Время, проходящее между двумя этими событиями, называется задержкой диспетчеризации.

Внешние прерывания также вызывают задержки. Внешние прерывания передаются напрямую в раздел. Когда операционная система вызывает гипервизор с запросом на ожидающее прерывание ( accept-pending-interrupt hypervisor ), гипервизор, при необходимости, выделяет виртуальный процессор на целевом разделе для обработки прерывания. Гипервизор предоставляет механизм организации очереди внешних прерываний, также связанных с виртуальными процессорами. При использовании механизма организации очереди возникают задержки.

Задержки не должны вызывать функциональных проблем, но могут негативно влиять на производительность приложений реального времени. Для оценки, в худшем случае задержка диспетчеризации составляет 18 миллисекунд, так как минимальный поддерживаемый цикл диспетчеризации на уровне виртуального процессора составляет одну миллисекунду. Эти цифры основаны на минимальной мощности раздела, составляющей 1/10 физического процессора и периоде вращения колеса распределения гипервизора в 10 миллисекунд. Их легко понять, если представить, что работа виртуального процессора распределена на первую и последнюю часть двух десятимиллисекундных интервалов. В общем случае, если эти задержки слишком велики, клиент может увеличить назначенную мощность, уменьшить число работающих виртуальных процессоров, не снижая мощности, или использовать разделы с выделенными процессорами.

Общий процессорный пул

В пуле находятся процессоры, не связанные с разделами, работающими на выделенных процессорах

Нет фиксированной связи между виртуальными и физическими процессорами

Гипервизор пытается использовать тот-же физический процессор

Для виртуализации процессоров необходима новая модель организации разделов, в корне отличная от модели, используемой в серверах с процессорами POWER4, где разделу назначается процессор целиком. В системах POWER4 разделы полностью владеют процессорами, и совместное их использование другими разделами невозможно. Такие разделы называются выделенными. В новой модели микроразделов физические процессоры абстрагируются в виртуальные, которые и выделяются разделам. Получившиеся виртуальные процессоры не могут использоваться совместно, однако физические процессоры оказываются в совместном пользовании, поскольку они преобразуются в виртуальные на уровне платформы. Такой принцип разделения является основной особенностью новой модели и реализуется автоматически. Подобные разделы называются совместно использующими процессор.