Состояние отечественных разработок в области высокопроизводительных вычислений

Микросхемы сигнальных процессоров серии "Мультикор"

Микросхемы сигнальных процессоров серии "Мультикор" [86] — это однокристальные программируемые многопроцессорные "системы на кристалле" на базе IP-ядерной (IP-intellectual property) платформы "Мультикор" [87], разработанной в ГУП НПЦ "ЭЛВИС".

Процессоры серии "Мультикор" сочетают в себе лучшие качества двух классов приборов: микроконтроллеров и цифровых процессоров обработки сигналов (DSP), что позволяет решать в рамках ограниченных габаритов одновременно обе задачи: управления и высокоточной обработки информации, включая сигналы и изображения.

Микросхемы спроектированы специалистами ГУП НПЦ "ЭЛВИС" совместно с центром проектирования "АНГСТРЕМ-М" (топологическое проектирование) и "АНГСТРЕМ-СБИС" (разработка блока PLL). Информация о микросхемах серии представлена в таблице 14.2.

В качестве процессорных блоков используются следующие типы IP-ядер из библиотеки платформы "Мультикор":

- процессорные RISC-ядра с архитектурой MIPS32, выполняющие функции центрального процессора системы CPU (Central Processing Unit);

- высокопроизводительные ядра процессоров-акселераторов для цифровой обработки сигналов (DSP — Digital Signal Processing) с плавающей/фиксированной точкой ELcore-xx (ELcore = Elvees's core).

Архитектура микросхем "Мультикор" по организации потоков данных и инструкций поддерживает пиковую производительность на большинстве задач обработки сигналов/изображений реального времени. Это обеспечивается малым количеством стадий процессорного конвейера, а также наличием многоканального интеллектуального контроллера DMA с поддержкой режимов самосинхронизации ресурсов микросхемы и 32/64-разрядного по данным порта внешней памяти со встроенным SDRAM/FLASH/SRAM/ROM-контроллером.

Микросхемы в зависимости от модели содержат от 2 до 8 Мбит внутренней памяти, периферийные SHARC-совместимые линки и последовательные порты, I2C, I2S, USB, Ethernet, PCI, UART, JTAG, а также ги-перлинки типа SpaceWire и Serial RapidIO.

Важным преимуществом отечественных микросхем является плотность кодов для DSP-ядер, которая характеризуется длиной программ для той или иной функции. Для микросхем серии "Мультикор" данная характеристика, как правило, лучше, чем у зарубежных аналогов ( таблица 14.4).

Команда для DSP-ядра имеет длину 32 или 64 бита и напоминает с этой точки зрения VLIW (Very Long Instruction Word). К примеру, одна 64-разрядная инструкция для ELcore-24 может выполнять две пары арифметических (логических) операций любой сложности и две пары пересылок типа "регистр-память". Это обеспечивает высокую плотность кодов для различных программ и позволяет реализовать различные функции обработки сигналов, используя в несколько раз меньше команд, чем для многих известных на рынке DSP-микросхем. Это обусловлено тем, что сравниваемые DSP имеют, к примеру, или огромную длину конвейера (10-12 уровней, как процессор TigerSHARC TS201), или низкую плотность кода. Например, число тактов для процедуры FFT-256 (комплексные 16-разрядные форматы данных и коэффициентов) в 8 раз короче для SISD-ядра ELcore-14 (менее 1000 тактов), чем для C54 разработки TI (8542 такта). За то же время 2SIMD ядро ELcore-24 может выполнять одновременно 2 таких преобразования, т. е. более чем в 16 раз быстрее по количеству тактов, чем ядро C54. Если обрабатываемый поток имеет двукратное распараллеливание, то ускорение обработки за счет 2SIMD-архитектуры автоматически равно 2. Для более сложной ситуации, без распараллеливания по данным, оценки ускорения даны в таблице 14.5.

Микросхема сигнального процессора 1892ВМ3Т

Микросхема сигнального процессора 1892ВМ3Т (MC-12) — это однокристальная двухпроцессорная "система на кристалле" (SOC) на базе IP-ядерной (IP-intellectual property) платформы "Мультикор" [84, 85].

Состав центрального процессора (CPU) следующий. Архитектура ядра, совместимая с MIPS32, имеет 32-битные шины передачи адреса и данных, кэш команд объемом 16 Кбайт, внутреннюю оперативную память объемом 64 Кбайт, аппаратные блоки умножения и деления. Обрабатываются 5 внешних запросов прерывания, в том числе немаскируемое прерывание (NMI). Производительность составляет 80 млн оп./с.

Поддерживается архитектура привилегированных ресурсов в стиле ядра R4000: регистры Count/Compare для прерываний реального времени, отдельный вектор обработки исключений по прерываниям.

Программируемое устройство управления памятью: два режима работы — с TLB (Translation Look aside Buffer) и FM (Fixed Mapped), 16 строк в режиме TLB.

Для отладки используются интерфейс JTAG IEEE 1149.1, встроенные средства отладки программ.

Цифровой сигнальный процессор (DSP) построен по "гарвардской" RISC-подобной архитектуре с оригинальной системой команд и преимущественно однотактным исполнением инструкций. Имеется SISD (Single Instructions Single Data) организация потоков команд и данных, 3-ступен-чатый конвейер по выполнению 32- и 64-разрядных инструкций. В состав сигнального процессора включены также память программ PRAM объемом 16 Кбайт, двухпортовые памяти данных RAM и YRAM объемом 96 и 48 Кбайт соответственно.

Процессор имеет стандартный набор инструкций, процедуры обработки и пересылки совмещаются.

Расширены возможности по динамическому диапазону обрабатываемых данных, позволяющие обрабатывать данные в 8/16/32-разрядных форматах с фиксированной точкой либо в одном из форматов с плавающей точкой — 24Е8 (стандарт IEEE 754) или 32Е16 (расширенный формат). Обеспечен компромиссный выбор между точностью и производительностью. Реализованы аппаратные меры повышения точности и динамического диапазона (блочная плавающая точка; режим насыщения; инструкции преобразования форматов).

Присутствует аппаратная поддержка программных циклов.

Пиковая производительность DSP:

- 240 млн оп./с 32-битных операций с плавающей точкой (IEEE 754);

- 1440 млн оп./с 8-битных операций с фиксированной точкой;

- 640 млн оп./с 16-битных операций с фиксированной точкой;

- 320 млн оп./с 32-битных операций с фиксированной точкой.

- шина данных — 32 разряда, шина адреса — 32 разряда;

- встроенный контроллер управления статической памятью типа SRAM, FLASH, ROM, а также синхронной памятью типа SDRAM. Возможно программное конфигурирование типа памяти и объема ее сегмента, программное задание циклов ожидания, формирование сигналов выборки 4 сегментов памяти, обеспечение обслуживания 4 внешних прерываний.

Периферийные устройства:

- 12-канальный контроллер прямого доступа в память (DMA). 4 внешних запроса прямого доступа. Специальные режимы синхронизации. Поддержка двумерной и разрядно-инверсной адресаций. Режим передачи Flyby, подобный реализованному в ADSP-TS201: внешнее устройство — внешняя память;

- два порта обмена последовательным кодом (SPORT), совместимые с ADSP21160 (разработка фирмы ADI);

- четыре линковых порта (LPORT), совместимые с ADSP21160. Имеется режим работы в качестве портов ввода-вывода общего назначения (GPIO);

- универсальный асинхронный порт (UART) типа 16550;

- набор таймеров — 32-разрядный интервальный таймер (IT), 32-разрядный таймер реального времени (RTT), 32-разрядный сторожевой таймер (WDT).

Реализованы дополнительные возможности и особенности:

- узел фазовой автоподстройки частоты (PLL) c умножителем/делителем входной частоты;

- встроенные средства отладки программ (OnCD);

- порт JTAG в соответствии со стандартом IEEE 1149.1.

Рассеиваемая мощность — около 1200 мВт (максимальная); режимы энергосбережения: 700 — при неработающем DSP-ядре (режим Stop); 70 — при программном уменьшении тактовой частоты в 16 раз; 30 — при программном отключении тактовой частоты (включение тактовой частоты осуществляется по внешним прерываниям).

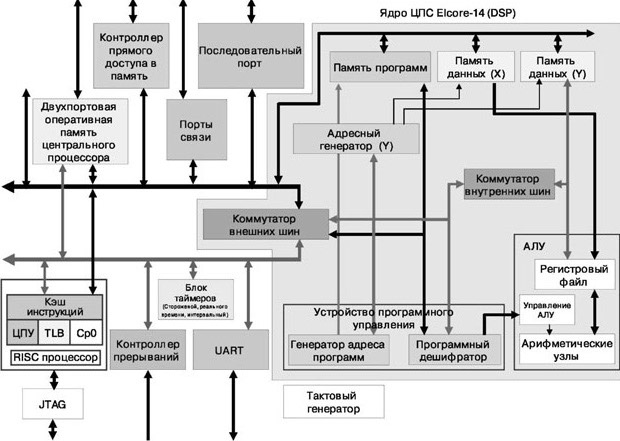

Структурная схема микросхемы 1892ВМ3T приведена на Рис. 14.2.

Состав процессора:

CPU — центральный процессор на основе RISC-ядра;

CRAM — двухпортовая оперативная память центрального процессора;

DSP — сопроцессор цифровой обработки сигналов с фиксированной точкой;

DMA — контроллер прямого доступа в память;

SPORT — последовательный порт;

UART — универсальный асинхронный порт;

ICACHE — кэш программ центрального процессора;

RTT — таймер реального времени;

A[31:0] — шина адреса порта внешней памяти;

D[31:0] — шина данных порта внешней памяти;

OnCD — встроенные средства отладки программ;

XRAM, YRAM — памяти данных DSP;

EDBS — коммутатор внешних шин;

IDBS — коммутатор внутренних шин;

PCU — устройство программного управления;

PAG — генератор адреса программ;

ALU — арифметическое устройство;

XDB0 — XDB3, GDB, PDB — шина данных DSP;

XAB, YAB, PAB — адресные шины DSP;

M, S, A, L — арифметические узлы ALU DSP.

CPU-ядро является ведущим в двухпроцессорной конфигурации микросхемы и выполняет основную программу. Для CPU-ядра обеспечен доступ к ресурсам DSP-ядра, являющегося ведомым по отношению к CPU-ядру: обмен данными CPU-ядра с ресурсами DSP-ядра выполняется по командам LOAD, STORE. Память DSP-ядра и его регистры для CPU-ядра — 32-разрядные (словные), то есть состояние двух младших разрядов адреса игнорируется.

CPU-ядро управляет работой DSP-ядра, передавая ему задание (макрокоманду). Затем запускает DSP-ядро, переводя его из режима STOP в режим RUN. С другой стороны, DSP-ядро формирует следующие прерывания в CPU-ядро: программное; по переполнению стека; при выполнении команды STOP; при достижении адреса останова при исполнении программы до адреса останова или завершении требуемого числа шагов при пошаговом исполнении программы.

мм

мм 18

18