|

приветствую создателей курса и благодарю за доступ к информации! понимаю, что это уже никто не исправит, но, возможно, будут следующие версии и было бы неплохо дать расшифровку сокращений имен регистров итд, дабы закрепить понимание их роли в общем процессе. |

Методы и средства отладки микропроцессорных систем

Логический анализатор

Как отмечалось выше, отладка современных микропроцессорных систем требует от инструментальных средств следующих возможностей:

- синхронный контроль состояния многоразрядных шин;

- регистрация последовательностей состояний в связи с редкими и однократными событиями;

- высокая частота работы.

Традиционные приборы контроля работы цифровых схем (амперметры, вольтметры, осциллографы, даже многолучевые с запоминанием информации) этим специфическим требованиям не удовлетворяют.

Для этих целей разработаны специальные устройства - логические анализаторы (ЛА). Основной областью применения ЛА является этап разработки МПС, когда отсутствуют и проверенная аппаратура, и отлаженные программы. Именно в этих условиях проявляются преимущества ЛА как универсального и гибкого в применении прибора, позволяющего разработчику находить причины сложных аппаратно-программных неисправностей.

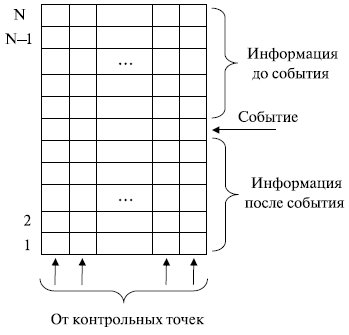

Основу логического анализатора составляет память логических последовательностей (ПЛП ). Тактовые сигналы записи в ПЛП могут вырабатываться внутренним генератором ЛА или поступать от контролируемой схемы. В последнем случае тактовые сигналы могут стробироваться другими внешними сигналами или их комбинацией. В случае заполнения всего объема ПЛП запись в нее продолжается циклически с нулевого адреса. Таким образом, в памяти всегда хранятся N последних принятых слов, где N - емкость ПЛП.

Режим регистрации продолжается до появления события, заданного оператором при настройке, или комбинации таких событий. Регистрация может быть прекращена не только непосредственно в момент события, но и через определенное число тактов после него. В этом случае в ПЛП фиксируются состояния сигналов в контрольных точках в моменты как предшествовавшие событию, так и непосредственно следовавшие за ним, что облегчает анализ ситуации (рис. 17.1). Количество тактов последействия также определяется при настройке.

Современные логические анализаторы имеют стандартные средства подключения к контролируемой МПС, большое разнообразие условий запуска по последовательности событий, наличие разнообразных режимов отображения информации, высокое быстродействие (до нескольких гигагерц), большую емкость ПЛП как по числу регистрируемых каналов (несколько сотен), так и по длине регистрируемой последовательности (десятки мегабит на канал). Некоторые модели логических анализаторов снабжаются встроенными генераторами тестовых последовательностей, что позволяет использовать их в качестве автономных приборов при поиске неисправностей в отдельных блоках МПС.

Сигнатурный анализатор

Поиск неисправности в МПС с помощью логического анализатора требует высокой квалификации персонала. Для каждой конкретной неисправности необходимо заново разрабатывать процедуру испытаний, настраивать прибор на новый режим работы, который, по мнению оператора, позволит обнаружить и локализовать неисправность. Поэтому ЛА используются в основном на этапе разработки МПС. В то же время он малопригоден на этапах производства и эксплуатации системы. Здесь большее распространение получили принципы сигнатурного анализа, которые, не требуя высокой квалификации персонала, позволяют быстро и точно отыскивать вышедший из строя компонент МПС с помощью недорогого и компактного оборудования.

Сигнатурный анализ основан на преобразовании длинных последовательностей двоичных сигналов в двоичное число, называемое сигнатурой. Измеряемые двоичные последовательности возбуждаются в контрольных точках МПС под действием специальной тестовой программы. Сигнатуры контрольных точек определяются на заведомо ра ботоспособной системе и указываются на принципиальной схеме МПС подобно тому, как на схемах аналоговых устройств указываются осциллограммы и некоторые параметры аналоговых сигналов. Сигнатура представляется, как правило, в виде нескольких шестнадцатеричных цифр.

В настоящее время в связи со все возрастающей интеллектуализацией устройств сигнатурные анализаторы постепенно утрачивают свои позиции.

JTAG-эмулятор

В последнее время компании - производители микропроцессоров и микроконтроллеров интегрируют в свои новые разработки модули с функциями встроенной отладки - отладчики на кристалле. Для поддержки функций встроенной отладки необходим специальный канал связи с компьютером. Чаще всего в качестве такого канала используется тестовый последовательный интерфейс типа JTAG, поэтому аппаратное средство отладки, построенное на базе встроенного в кристалл отладочного модуля, часто называют JTAG-эмулятором. Аббревиатура JTAG возникла по наименованию разработчика - объединенной группы по тестам JoINT Test Action Group.

Интерфейсом JTAG, реализованным согласно стандарту IEEE 1149.1-2001, управляет одно устройство-контроллер (чаще всего это персональный компьютер, оснащенный соответствующим программным обеспечением и интерфейсным адаптером), к которому может быть подключено несколько тестируемых устройств.

В состав интерфейса JTAG входят 5 однонаправленных последовательных линий связи (один из сигналов необязательный). Эти сигналы образуют тестовый порт ТАР (Test Access Port), через который тестируемое устройство подключается к тестирующему оборудованию (контроллеру).

В задачу тестирующего оборудования входит формирование тестовых сигналов по программе тестирования, определенной разработчиком тестируемого устройства, и сравнение полученных результатов с эталонами.

Один и тот же контроллер и порт могут использоваться для тестирования любого числа устройств, поддерживающих JTAG. Для этого устройства своими портами ТАР соединяются в цепочку. Стандартизованный логический формат позволяет контроллеру независимо общаться с каждым из устройств цепочки.

JTAG-эмулятор позволяет выполнять следующие действия:

- Пошаговый (на уровне машинных команд) режим выполнения программы.

- Заморозка периферии при останове: в момент перехода в режим останова выполнения программы пользователя JTAG-эмулятор блокирует источник тактовой частоты, управляющий работой центрального процессора и периферийных устройств. Это обеспечивает точное отслеживание модельного времени. JTAG-эмулятор обеспечивает точное соответствие времени выполнения программы пользователя времени работы периферийных устройств.

- Доступ к ресурсам микроконтроллера при останове: JTAG-эмулятор предоставляет доступ ко всем ресурсам микроконтроллера в режиме останова выполнения программы пользователя.

Поскольку информация вводится в отлаживаемое устройство и выводится из него через последовательный порт, метод JTAG не может служить заменой полнофункциональному эмулятору, так как не в состоянии отразить текущее состояние внутренних шин.

Однако он имеет ряд очевидных достоинств:

- Низкая стоимость средства отладки: в простейшем случае JTAGэмулятор может состоять из кабеля, соединяющего порт компьютера с JTAG-портом на отлаживаемой плате. Все режимы отладки микроконтроллера поддерживаются программным обеспечением.

- Максимально точное соответствие условий отладки рабочим условиям серийного изделия: отладка МПС может осуществляться на серийной плате, дополненной только 5-контактным разъемом порта ТАР на серийном МП. Как следствие, электрические и временные характеристики системы в процессе отладки абсолютно идентичны характеристикам рабочего режима.

- Возможность одновременного тестирования нескольких устройств, объединенных JTAG-цепочкой, причем стандарт не вводит никаких ограничений на количество устройств в цепочке.

К недостаткам JTAG -эмулятора относятся следующие:

- Необходимое условие использования JTAG-эмулятора - наличие встроенной в микроконтроллер Flash-памяти программ, поскольку для загрузки программы пользователя при отладке JTAG-эмулятор задействует собственную память микроконтроллера. В микроконтроллерах, у которых применяется другой тип памяти программ (например, только ППЗУ), реализация JTAG-эмулятора на кристалле невозможна.

- JTAG-эмулятор имеет ограниченное (обычно не более 8) количество точек останова.

- Трудности в реализации пошагового режима на уровне операторов языка высокого уровня, так как для отработки этого режима в исходный текст отлаживаемой программы в начале каждого оператора ЯВУ должна вставляться команда вызова отладочного монитора, а количество контрольных точек ограниченно.

- Программа пользователя, которая загружается для отладки, имеет больший размер и большее времен выполнения, чем рабочая программа, в связи с необходимостью вставки в нее команд вызова отладочного монитора. Это нарушает, хотя и несущественно, масштаб реального времени выполнения программы пользователя в режиме отладки с JTAG-эмулятором.

- JTAG-эмулятор не поддерживает точки останова по сложным (комплексным) условиям, которые реализованы, например, во внутрисхемных эмуляторах.

JTAG широко используется для отладки реальных устройств. Тестируемая программа может быть той окончательной версией (после удаления команд вызова монитора отладки), которая будет поставляться.

Интерфейс JTAG применяется не только для тестирования, но и для программирования различных устройств, в том числе и энергонезависимой памяти микроконтроллеров. Контакты для сигналов JTAG имеются на шине PCI, однако в их использовании единообразия не наблюдается (либо остаются неподключенными, либо соединяются для организации цепочки).

Отметим, что интерфейсом JTAG в настоящее время оснащаются не только однокристальные микроконтроллеры и сигнальные процессоры, но и универсальные микропроцессоры вплоть до моделей с наивысшей на сегодняшний день производительностью, например, Intel Core i7

ExTReme Edition. Здесь он позволяет не только тестировать сам процессор (это не представляет особого прикладного интереса), но и организовать зондовый режим отладки (probe mode). Зондовый режим является мощным средством отладки системного программного обеспечения; обычный процессор, связанный с тестовым контроллером интерфейсом JTAG, превращается во внутрисхемный эмулятор.