|

Добрый день!

Скажите, пожалуйста,планируется ли продолжение курсов по нанотехнологиям? Спасибо, Евгений

|

Оценка производительности и живучести МКМД-БИТ-потокового предпроцессора системы астронавигации

Модуль подавления реакций медианного фильтра на паразитные межстрочные положения " скользящего окна " ( CMZ 4(128) - рис. 8.14) представляет собой генератор циклической константы вида: 4 "нуля" и 124 "единицы", которая стробирует по "И" результирующее изображение, обнуляя в нем 2 первых и 2 последних пикселя в каждой строке.

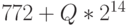

Модуль CMZ 4(128) представляет собой делитель частоты CG на основе циклической константы вида  (БП (2, 1), настроенный на бит-инструкцию CG ). Выход генератора циклического строба SG (БП (1, 11, 3)) опережает по фазе на 2 такта момент появления первого пикселя результирующего изображения на выходе медианного фильтра и в данном случае составляет 616(+2*128) тактов.

(БП (2, 1), настроенный на бит-инструкцию CG ). Выход генератора циклического строба SG (БП (1, 11, 3)) опережает по фазе на 2 такта момент появления первого пикселя результирующего изображения на выходе медианного фильтра и в данном случае составляет 616(+2*128) тактов.

Соотношение фаз управляющего и обрабатываемых потоков поддерживается подстановкой бит-инструкций AND или NAND в бит-процессоры первой строки, и они должны редактироваться при любом пространственном перемещении как модуля медианной фильтрации, так и/или модуля подавления реакций на паразитные положения "скользящего окна". Модуль CMZ 4(128) генерирует циклическую константу  , в которой 4 "единичных" бита, а остальные - "нули". Этот модуль вносит только один такт в общую задержку во всем предшествующем тракте обработки, и поэтому суммарное время задержки в субпроцессоре по его выходу (БП (1, 11, 2)) составляет 619(+2*128) тактов.

, в которой 4 "единичных" бита, а остальные - "нули". Этот модуль вносит только один такт в общую задержку во всем предшествующем тракте обработки, и поэтому суммарное время задержки в субпроцессоре по его выходу (БП (1, 11, 2)) составляет 619(+2*128) тактов.

В модуле CMZ 4(128) в одном 8-битном цикле выполняются (рис. 8.15):

- 1 генерация циклической константы и 2 пересылки в задающем генераторе NG (БП (2, 1));

- 1 формирование (модификация) циклической константы

в блоке CG (БП с первого по восьмой столбец бит-матрицы) и 1 пересылка;

в блоке CG (БП с первого по восьмой столбец бит-матрицы) и 1 пересылка; - 1 формирование циклической константы

в модуле SG методом слияния по трем "ИЛИ" (с задержкой) циклической константы

в модуле SG методом слияния по трем "ИЛИ" (с задержкой) циклической константы  (БП девятого столбца бит-матрицы), инверсия циклической константы

(БП девятого столбца бит-матрицы), инверсия циклической константы  (БП (1, 10)) и 3 пересылки,

(БП (1, 10)) и 3 пересылки, - фильтрация входного потока (БП (1, 11)) в блоке AND и 2 пересылки.

Рис. 8.15. Топологическая схема модуля подавления паразитных реакций медианного фильтра (CMZ 4(128))

Таким образом, пропускная способность модуля подавления паразитных реакций медианного фильтра по потоку 8 -битных слов-инструкций составляет ![V_{I} = [(1+2)+(1+1)+(3+3)+(1+2)]*F_{t} /8 = 14*F_{t} /8 = 1,75*F_{t}](/sites/default/files/tex_cache/bb5b52f180cbe8b45a7b1ebc441cdca2.png) , а из 14 реально исполняемых в режиме интерпретации слов-инструкций полезными для пользователя являются три: формирование строба

, а из 14 реально исполняемых в режиме интерпретации слов-инструкций полезными для пользователя являются три: формирование строба  , подавление паразитной реакции и пересылка результата.

, подавление паразитной реакции и пересылка результата.

Модуль формирования построчных гистограмм отфильтрованного бинарного изображения и их циклического сглаживания 2-элементным " скользящим окном " ( LHM ) является первым в канале арифметической обработки субпроцессора. Модуль LHM осуществляет подсчет количества "единичных" пикселей в каждой строке и попарное суммирование (сглаживание гистограммы) накопленных сумм из двух смежных строк, принадлежащих одному кадру обрабатываемого изображения. Модуль LHM (рис. 8.16) содержит:

- циклический накапливающий сумматор (ADDA) двоичной последовательности до 124 бит или, что одно и то же, пикселей, который состоит из четырехкаскадного сумматора ADD и сумматора-накопителя ADDR;

- блок управления (CADDA16(128)) циклом накопления, который генерирует циклическую управляющую константу, содержащую 16 "единиц" и 112 "нулей";

- блок циклического сглаживания (DWH) построчной гистограммы 2-элементным "скользящим окном".

В четырех каскадах потокового сумматора ADD сначала попарно складывается содержимое четных и нечетных бит, выделенных из обрабатываемого потока. Затем по аналогичной схеме суммируются четные и нечетные 2-битные операнды, выделенные из обрабатываемого потока, и т. д. до получения 16-битных операндов (с 8 значащими разрядами), которые уже суммируются в ADDR по классической схеме накопления в аккумуляторе с управляемым циклом.

Потоковая часть сумматора ADD (рис. 8.17) занимает с 20-го по 28-й столбцы бит-матрицы и имеет только информационный вход (3, 28, 4) с начальной задержкой 619(+2*128) тактов.

Все локальные блоки управления ADD распределены по сумматору, и с их помощью один поток из каждого предшествующего каскада суммирования расщепляется в пространстве на два потока, которые затем выравниваются по времени задержки и суммируются. Для этих целей в первом каскаде используется меандр (и его инверсия) вида …0101…01, во втором каскаде - … 00110011…0011 и т. д. Выход потоковой части сумматора ADD расположен в бит-процессоре (1, 20, 1), где общее время задержки составляет 647(+2*128) тактов.

Рис. 8.16. Структурная схема модуля формирования построчной гистограммы обрабатываемого изображения (LHM)

Аккумулирующая часть сумматора ADDR16 (рис. 8.17) занимает с 15-го по 19-й БП первой строки бит-матрицы, а блок управления циклом накопления CADDA16(128) - с 5-го по 18-й столбец 2-й и 3-й строки бит-матрицы. Этот блок частично пересекается по топологии с блоком DWH сглаживания гистограммы 2-элементным "скользящим окном".

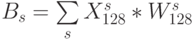

Сумматор-накопитель ADDR16 с 16-битным аккумулятором имеет 2 информационных входа: (1, 18, 3) и (1, 20, 1), 2 управляющих входа: "чтение" ( R ) - (1, 17, 2) и "сброс" ( RS ) - (2, 18, 2), и 1 информационный выход - (2, 17, 1) с общим временем задержки от входа субпроцессора в 771(+2*128) тактов. В данном случае полный цикл накопления составляет 128 тактов и задается 16-битным "единичным" стробом "чтение": 16 "единиц" и 112 "нулей", инверсия которого используется для обнуления содержимого аккумулятора.

Блок управления циклом накопления CADDA16(128) построчной гистограммы представляет собой:

- задающий генератор (LG) в виде счетчика до 27 тактов (2-я и 3-я строки бит-матрицы в пределах с 5-го по 12-й столбец);

увеличить изображение

Рис. 8.17. Топологическая схема модуля формирования построчной гистограммы обрабатываемого изображения (LHM) - управляемый генератор (PG) в виде счетчика до 24 тактов (2-я и 3-я строки бит-матрицы в пределах 13-го и 14-го столбцов). Собственно управляющий 16-битный "единичный" строб "чтение" формируется БП (1, 14, 3), настроенном на бит-инструкцию ST1. В этой бит-инструкции на 2-й управляющий вход (снизу) подается циклическая константа

, а на 1-й информационный вход (слева) - циклическая константа

, а на 1-й информационный вход (слева) - циклическая константа  . Данный строб используется в БП (2, 17), обеспечивая циклическое "чтение" накопленной суммы, а его инверсия используется в БП (1, 18) для циклического обнуления содержимого аккумулятора.

. Данный строб используется в БП (2, 17), обеспечивая циклическое "чтение" накопленной суммы, а его инверсия используется в БП (1, 18) для циклического обнуления содержимого аккумулятора.

Блок циклического сглаживания DWH2 построчной гистограммы 2-элементным "скользящим окном" представляет собой сумматор двух смежных операндов с задержкой предыдущего на 128 тактов. На топологической схеме рис. 8.17 он занимает БП: четыре первых столбца полностью, с 5-го по 11-й в первой строке и с 5-го по 10-й в четвертой строке бит-матрицы. Первый значащий результат на его выходе (БП (1, 11, 2)) появляется на 900-м такте после полного первого цикла суммирования для данного кадра обрабатываемого изображения (без учета времени начальной задержки на 2*128 тактов в модуле генерации тест-данных).

Предшествующий ему цикл срабатывания 2-элементного "скользящего окна" соответствует  такту и используется в канале обнаружения отказов, так как имеет заранее известное содержимое, отвечающее реакции на две тестовые строки. Здесь

такту и используется в канале обнаружения отказов, так как имеет заранее известное содержимое, отвечающее реакции на две тестовые строки. Здесь  - индекс кадра обрабатываемого изображения. В основном канале обработки реакция 2-элементного "скользящего окна" на этом цикле обнуляется управляющим блоком ( DWHCU ), который на топологической схеме совмещен с модулем свертки вектор-столбца SMM.

- индекс кадра обрабатываемого изображения. В основном канале обработки реакция 2-элементного "скользящего окна" на этом цикле обнуляется управляющим блоком ( DWHCU ), который на топологической схеме совмещен с модулем свертки вектор-столбца SMM.

Из приведенных данных видно, что в модуле формирования построчной гистограммы обрабатываемого изображения ( LHM) в одном 16 -битном цикле выполняются:

- в циклическом накапливающем сумматоре (ADDA): в каждом из четырех каскадов сумматора ADD - 1 суммирование, 2 операции "И", 1 операция генерации константы и 6 пересылок, а в сумматоре-накопителе ADDR - 1 суммирование, 2 операции "И" и 6 пересылок;

- в блоке управления CADDA16(128): 4 генерации циклической константы

, 8 ее пересылок, 1 генерация циклической константы

, 8 ее пересылок, 1 генерация циклической константы  и 1 ее пересылка, 1 генерация или проверка условия формирования циклической константы

и 1 ее пересылка, 1 генерация или проверка условия формирования циклической константы  и 1 ее "пересылка", 1 цикл формирования константы

и 1 ее "пересылка", 1 цикл формирования константы  ;

; - в блоке циклического сглаживания (DWH): 8 пересылок в FIFO-регистровой линии задержки, 1 сложение и 1 пересылка результата.

Таким образом, пропускная способность модуля формирования построчной гистограммы обрабатываемого изображения ( LHM) по потоку смеси из 2-, 4-, 8- и 16- битных слов-инструкций составляет:

![V_{I} = [4*(1+2+1+6)+(1+2+1+6)+(4+8+1+1+1+1+1)+(8+1+1)]*F_{t} /16 = 76*F_{t}/16 = 4,75*F_{t} ,](/sites/default/files/tex_cache/32dc9fb04d365665cf35fbce252e1479.png)

а из 76 эквивалентных 16-битных и реально исполняемых в режиме интерпретации слов-инструкций полезными для пользователя являются только 7 операций: суммирование с накоплением, сглаживание двухэлементным "скользящим окном", управление циклом суммирования и четыре пересылки операндов.

Модуль " свертки " вектор-столбца построчной гистограммы отфильтрованного изображения ( SMM - рис. 8.18) осуществляет "взвешенное" суммирование  элементов

элементов  построчной гистограммы

(в данном случае

построчной гистограммы

(в данном случае  ), умноженной на соответствующий весовой коэффициент

), умноженной на соответствующий весовой коэффициент  , представляющий собой номер строки в исходном изображении.

, представляющий собой номер строки в исходном изображении.

Следует помнить, что и множимое  , и множитель

, и множитель  имеют только 7 значащих разрядов. Поэтому их произведение имеет только 14 значащих разрядов. Сам весовой коэффициент

имеют только 7 значащих разрядов. Поэтому их произведение имеет только 14 значащих разрядов. Сам весовой коэффициент  изменяется (по

изменяется (по  ) от 0 до 127, что позволяет непосредственно в умножителе подавить паразитные взаимодействия межу кадрами при обработке 2-элементным "скользящим окном" построчной гистограммы каждого кадра исходного изображения. Данный модуль включает:

) от 0 до 127, что позволяет непосредственно в умножителе подавить паразитные взаимодействия межу кадрами при обработке 2-элементным "скользящим окном" построчной гистограммы каждого кадра исходного изображения. Данный модуль включает:

- 8-разрядный умножитель (ML) положительных чисел;

- блок генерации весовых коэффициентов (WGU) "свертки" вектор-столбца построчной гистограммы;

- блок генерации циклической константы

(CCU1(128));

(CCU1(128)); - накапливающий сумматор оператора свертки вектор-столбца (ADDRV32);

- блок управления (CADDR32) циклом накопления оператора свертки ADDRV32 и аналогичным циклом в сумматоре-накопителе построчной гистограммы ADDRH32; этот блок генерирует циклическую управляющую константу, содержащую 32 "единицы" и (214-32) "нулей";

- накапливающий сумматор построчной гистограммы (ADDRH32);

- блок обнуления (DWHCU) паразитных взаимодействий строк из разных кадров, попавших в одно 2-элементное "скользящее окно".

Умножитель ML занимает первые 9 столбцов бит-матрицы рис. 8.19-a и имеет два информационных входа (БП (2, 3, 1) - множитель и БП (3, 3, 4) - множимое) и один управляющий (БП (1, 3, 1)).