Задача логического вывода и когерентность кэш-памяти в ВС SPMD-архитектуры

Применение механизма предикатов в ВС SPMD-архитектуры

Предикатные вычисления предполагают наличие памяти для хранения булевых переменных: результатов логических операций сравнения, отношения, проверки условий и т.д., в общем случае — результата проверки истинности некоторого высказывания. Система команд предполагает спекулятивный режим выполнения операций. Этот режим обеспечивает выполнение команды или задержку ее выполнения, а также пропуск команд в зависимости от значения некоторого предиката, соотнесенного этой команде. Адрес предиката указывается в соответствующих разрядах командного слова.

В зависимости от кода операции, в случае, если указанный в команде предикат имеет значение 0 (ЛОЖЬ), выполнение команды задерживается (предикат опрашивается в режиме "жужжания") или пропускается. Пропуск означает выполнение следующей команды.

Пусть система команд процессора ВС предполагает наличие разрядов  командного слова, в которых указывается адрес предиката; по нулевому его значению команда

инициализируется в режиме "жужжания", но не выполняется до смены

значения предиката другим процессором.

командного слова, в которых указывается адрес предиката; по нулевому его значению команда

инициализируется в режиме "жужжания", но не выполняется до смены

значения предиката другим процессором.

Возьмем пример свертки массива в разделе 12.2.1 при тех же значениях k = 10, N = 4.

Рассмотрим массив 2k-2 логических предикатов  ,

по числу исходных и промежуточных данных, участвующих в качестве операндов в выполнении операции

свертки массива (рис. 13.3). В примере это — операция умножения.

,

по числу исходных и промежуточных данных, участвующих в качестве операндов в выполнении операции

свертки массива (рис. 13.3). В примере это — операция умножения.

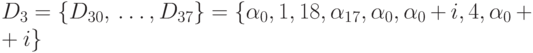

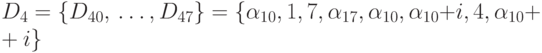

Поставим в соответствие массиву предикатов дескрипторы D3 и D4, имеющие в памяти каждого процессора начальный вид

.

.

.

.

План программы следующий. Пусть сначала все предикаты имеют значение 1 (ИСТИНА). С этими значениями разрешим выполнение первых пяти умножений. Однако прежде чем их выполнять, присвоим значение 0 (ЛОЖЬ) тем предикатам, которые соответствуют результатам операции умножения. Поскольку такую операцию выполнят все процессоры, то те из них, которые попытаются выполнить умножение еще не найденных промежуточных результатов, окажутся в состоянии ожидания этих результатов. По выполнении умножения присвоим значение 1 (ИСТИНА) тем же предикатам, каким ранее присваивалось значение 0. Так реализуется частичная упорядоченность работ во времени.

Программа представлена в таблице 13.3.

Выполнение команд 0 и 1 не отличается от выполнения аналогичных команд в табл. 12.1.

По команде 2 предикату, адрес которого указан в дескрипторном элементе D47,

присваивается значение 0. Таким образом, процессор 0 первый раз присвоит это

значение предикату  . Процессор 1 первый раз присвоит

это значение предикату

. Процессор 1 первый раз присвоит

это значение предикату  и т.д.

и т.д.

По командам 3, 4 и 5 производится умножение соседних элементов расширенного

массива. Разбиение команды (имитация одноадресной системы команд) обусловлено

необходимостью организации спекулятивного режима раздельного использования

каждого множителя в зависимости от соответствующего ему предиката. А именно,

возможность использования первого множителя, адрес которого указан в

дескрипторном элементе D17, связана со значением предиката,

адрес которого указан в дескрипторном элементе D37. Это определяет

возможность считывания. Первый раз по команде 3 процессор 0 произведет считывание, т.к.  . Произведут считывание и другие процессоры, т.к.

. Произведут считывание и другие процессоры, т.к.  .

.

По команде 4 изменяется адрес предиката для использования следующего элемента расширенного массива в качестве второго множителя.

По команде 5 завершается операция умножения. Однако ее выполнение теперь

зависит от значения предиката, соответствующего второму множителю. Первый раз для

процессора 0 это предикат  .

.

По команде 6 восстанавливается значение 1 предиката, которому по команде 2 присваивалось значение 0.

По команде 7 восстанавливается значение D37, скорректированное по команде 4.

Остальные команды аналогичны рассмотренным ранее (табл. 12.1).